# CIRCUITOS DIGITAIS E MISTOS CMOS COM APLICAÇÃO EM MEDIDOR DE ENERGIA

Thiago Brito Bezerra

Tese de Doutorado apresentada ao Programa de Pós-graduação em Engenharia Elétrica, COPPE, da Universidade Federal do Rio de Janeiro, como parte dos requisitos necessários à obtenção do título de Doutor em Engenharia Elétrica.

Orientador: Antonio Petraglia

Rio de Janeiro Junho de 2017

# CIRCUITOS DIGITAIS E MISTOS CMOS COM APLICAÇÃO EM MEDIDOR DE ENERGIA

#### Thiago Brito Bezerra

TESE SUBMETIDA AO CORPO DOCENTE DO INSTITUTO ALBERTO LUIZ COIMBRA DE PÓS-GRADUAÇÃO E PESQUISA DE ENGENHARIA (COPPE) DA UNIVERSIDADE FEDERAL DO RIO DE JANEIRO COMO PARTE DOS REQUISITOS NECESSÁRIOS PARA A OBTENÇÃO DO GRAU DE DOUTOR EM CIÊNCIAS EM ENGENHARIA ELÉTRICA.

| Examinada por: |                                                     |

|----------------|-----------------------------------------------------|

|                |                                                     |

|                | Prof. Antonio Petraglia, Ph.D.                      |

|                | Prof. Antonio Carneiro de Mesquita Filho, Dr.d'État |

|                | Prof. José Gabriel Rodríguez Carneiro Gomes, Ph.D.  |

|                | Prof. Marcio Nogueira de Souza, D.Sc.               |

|                | Prof. Sebastian Yuri Cavalcanti Catunda, D.Sc.      |

RIO DE JANEIRO, RJ – BRASIL JUNHO DE 2017 Bezerra, Thiago Brito

Circuitos digitais e mistos CMOS com aplicação em medidor de energia/Thiago Brito Bezerra. – Rio de Janeiro: UFRJ/COPPE, 2017.

XVI, 87 p.: il.; 29,7cm.

Orientador: Antonio Petraglia

Tese (doutorado) – UFRJ/COPPE/Programa de Engenharia Elétrica, 2017.

Referências Bibliográficas: p. 83 – 87.

Circuitos digitais e mistos.

Circuitos a capacitores chaveados.

Modulador sigma-delta.

CMOS. I. Petraglia, Antonio. II. Universidade Federal do Rio de Janeiro, COPPE, Programa de Engenharia Elétrica.

III. Título.

Aos meus pais, Francisco e Graça, e aos meus irmãos, Marco, Jósimo e Thomás, pelo apoio durante toda minha jornada acadêmica.

## Agradecimentos

Agradeço ao meu orientador, o professor Dr. Antonio Petraglia pela orientação e ensinamentos transferidos durante o período de execução deste trabalho.

Aos professores do Departamento de Engenharia Elétrica que contribuíram com a minha formação científica durante o período do doutorado.

Aos meus pais, que sempre se empenharam ao máximo para que meus irmãos e eu recebêssemos uma boa educação.

A minha namorada, Thaís, pelo amor, compreensão e incentivo.

Ao Alex, Luciana e Isabela por terem me acolhido em seu lar como um membro da família.

Aos amigos do Laboratório de Processamento Analógico e Digital de Sinais do Programa de Engenharia Elétrica da COPPE/UFRJ: Allan, Fabian, Fernanda, Pedro, João, Jorge, Oscar, Genildo, Gustavo e Fábio, pelo apoio e debate sobre o projeto.

À Universidade Federal do Amazonas pela liberação, assim podendo me dedicar em tempo integral a conclusão do doutorado.

E ao CNPQ pelo apoio financeiro.

Resumo da Tese apresentada à COPPE/UFRJ como parte dos requisitos necessários para a obtenção do grau de Doutor em Ciências (D.Sc.)

# CIRCUITOS DIGITAIS E MISTOS CMOS COM APLICAÇÃO EM MEDIDOR DE ENERGIA

Thiago Brito Bezerra

Junho/2017

Orientador: Antonio Petraglia

Programa: Engenharia Elétrica

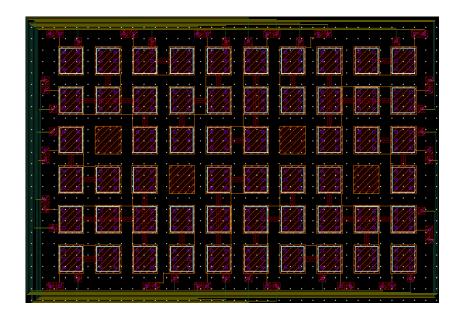

O projeto de circuitos integrados CMOS digitais e mistos para medidores de energia se mostra necessário em aplicações nas quais se deseja diagnosticar sistemas de medição de energia elétrica com rapidez de processamento e/ou baixo consumo de potência. O grande desafio está em compreender o seu funcionamento e investigar topologias e/ou metodologias de projeto que permitam solucionar as dificuldades no projeto de circuitos integrados digitais e mistos, com o objetivo de otimizar o compromisso entre rapidez de processamento, potência consumida e área ocupada. Neste trabalho apresentamos o desenvolvimento de novos circuitos digitais e mistos para serem utilizados em um medidor de energia. Os circuitos digitais se utilizam de uma técnica de desvio que evita cálculos redundantes. Essa técnica foi aplicada no multiplicador de baixo consumo, reduzindo seu consumo em 40%. Já para o filtro passa-altas, o consumo foi reduzido em 15%. E o filtro passa-baixas teve o consumo reduzido em 26%. Um modulador sigma delta pseudo-paralelo foi otimizado ao nível do sistema para atingir o SNR máximo usando valores de capacitância mínimos para que os requisitos de velocidade dos blocos analógicos pudessem ser aliviados para reduzir o consumo de energia. O PSDM desenvolvido foi verificado por simulações pós-leiaute, atingindo uma faixa dinâmica de 99,8 dB para uma largura de banda do sinal de 2 kHz, com uma razão de sobre-amostragem de 128, ocupando uma área de  $0.16 \text{ mm}^2$  e consumindo apenas  $52.5 \mu W$ .

Abstract of Thesis presented to COPPE/UFRJ as a partial fulfillment of the requirements for the degree of Doctor of Science (D.Sc.)

# DIGITAL AND MIXED CMOS CIRCUITS WITH ENERGY METER APPLICATION

Thiago Brito Bezerra

June/2017

Advisor: Antonio Petraglia

Department: Electrical Engineering

The design of digital and mixed CMOS integrated circuits for energy meters is required in applications where energy measurement systems are installed with fast processing and low power consumption. The great challenge is to understand its operation and investigate topologies and/or design methodologies that allow to solve the difficulties in the design of integrated digital and mixed circuits, in order to find a good compromise between processing speed, power consumed and occupied area. In this work we present the development of new digital and mixed circuits to be used in an energy meter. The digital circuits uses a bypassing technique which avoids redundant calculations. This technique was applied in the low power multiplier, reducing its consumption by 40%. For the high-pass filter, the power consumption was reduced by 15%. And the low-pass filter had the consumption reduced by 26%. A pseudo-parallel sigma-delta modulator that was optimized at system level to attain maximum SNR using minimum capacitance values so that speed requirements of the analog blocks could be alleviated in order to reduce power consumption. The developed PSDM was verified by post-layout simulations, reaching a dynamic range of 99.8 dB for a signal bandwidth of 2 kHz, with an oversampling ratio of 128, occupying an area of 0.16 mm<sup>2</sup> and consuming only 52.5  $\mu$ W.

# Sumário

| Li | sta c          | le Figu  | ıras                                                | X    |

|----|----------------|----------|-----------------------------------------------------|------|

| Li | sta c          | le Tab   | elas                                                | xiii |

| Li | sta c          | le Abr   | reviaturas                                          | xv   |

| 1  | Inti           | roduçã   | .0                                                  | 1    |

|    | 1.1            | Motiv    | ração                                               | . 2  |

|    | 1.2            | Objet    | ivos                                                | . 5  |

|    | 1.3            | Estru    | tura do Texto                                       | . 6  |

| 2  | Mu             | ltiplica | ador com Baixo Consumo                              | 7    |

|    | 2.1            | Técni    | ca de Desvio                                        | . 8  |

|    | 2.2            | Circui   | ito Multiplicador 16x16                             | . 11 |

| 3  | Filt           | ros Di   | gitais                                              | 13   |

|    | 3.1            | Filtro   | Passa-Altas                                         | . 14 |

|    | 3.2            | Filtro   | Passa-Baixas                                        | . 17 |

| 4  | Mo             | dulado   | or Sigma-Delta Pseudo-Paralelo                      | 20   |

|    | 4.1            | PSDN     | I de Baixa Sobre-Amostragem                         | . 22 |

|    | 4.2            | Imple    | mentação de um PSDM de Segunda Ordem e com Fator de |      |

|    |                | Desen    | rolamento Dois                                      | . 24 |

|    | 4.3            | Mode     | lagem do PSDM                                       | . 26 |

|    |                | 4.3.1    | Resposta do PSDM Ideal                              | . 28 |

|    |                | 4.3.2    | Resposta do PSDM Não-Ideal                          | . 30 |

| 5  | $\mathbf{Pro}$ | jeto d   | o PSDM                                              | 32   |

|    | 5.1            | Circui   | itos a Capacitores Chaveados                        | . 32 |

|    | 5.2            | Proje    | to em Nível de Transistores                         | . 35 |

|    |                | 5.2.1    | Circuitos Digitais                                  | . 35 |

|    |                | 5.2.2    | Gerador de Fases do Relógio                         | . 36 |

|    |                | 5 2 3    | Chave CMOS                                          | 37   |

|              |       | 5.2.4   | Amplificador Operacional de Transcondutância                | 39 |

|--------------|-------|---------|-------------------------------------------------------------|----|

|              |       | 5.2.5   | Quantizador                                                 | 44 |

|              |       | 5.2.6   | Conversor Digital para Analógico                            | 45 |

|              |       | 5.2.7   | Coeficientes da Saída                                       | 46 |

|              |       | 5.2.8   | Modulador Completo                                          | 47 |

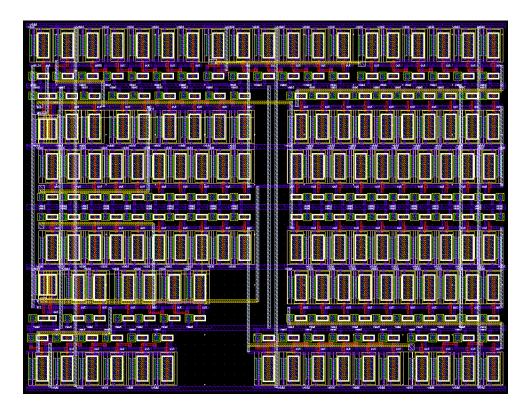

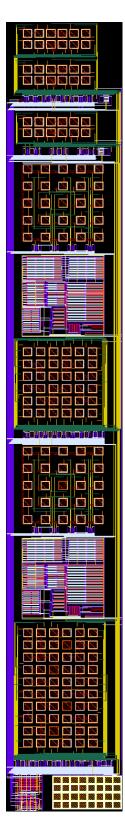

| 6            | Leia  | aute de | o PSDM                                                      | 51 |

|              | 6.1   | Leiaut  | te dos Circuitos Digitais Básicos                           | 51 |

|              |       | 6.1.1   | Leiaute da Porta Lógica Inversora                           | 51 |

|              |       | 6.1.2   | Leiaute da Porta Lógica NOR                                 | 52 |

|              |       | 6.1.3   | Leiaute do Gerador de Fases do Relógio                      | 52 |

|              |       | 6.1.4   | Leiaute da Chave CMOS                                       | 53 |

|              |       | 6.1.5   | Leiaute do MUX 2x1                                          | 54 |

|              | 6.2   | Leiaut  | te dos Capacitores                                          | 54 |

|              |       | 6.2.1   | Leiaute da Matriz do Circuito de Controle da Tensão de Modo |    |

|              |       |         | Comum                                                       | 55 |

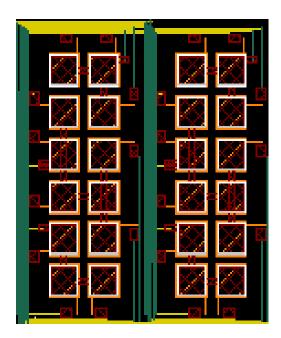

|              |       | 6.2.2   | Leiaute da Matriz do Primeiro Integrador                    | 56 |

|              |       | 6.2.3   | Leiaute da Matriz do Segundo Integrador                     | 58 |

|              |       | 6.2.4   | Leiaute das Matrizes dos Coeficientes de Saída              | 59 |

|              | 6.3   | Leiaut  | te do Amplificador Operacional de Transcondutância          | 62 |

|              | 6.4   | Leiaut  | te do Quantizador                                           | 63 |

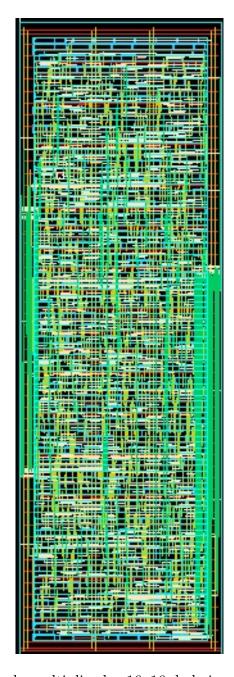

|              | 6.5   | Leiaut  | te do Modulador Completo                                    | 64 |

| 7            | Res   | ultado  | os das Simulações                                           | 66 |

|              | 7.1   | Simul   | ações em Nível de Transistores                              | 67 |

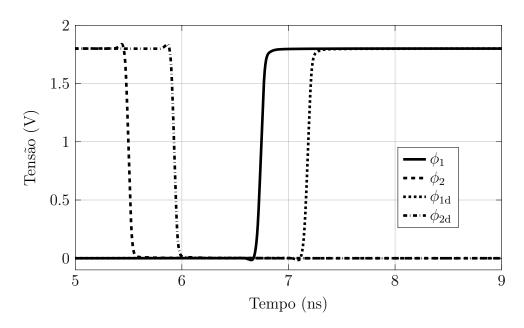

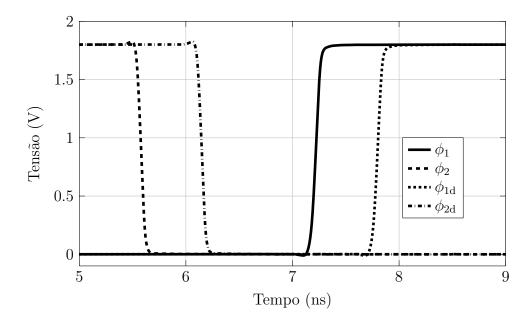

|              |       | 7.1.1   | Gerador de Fases do Relógio                                 | 67 |

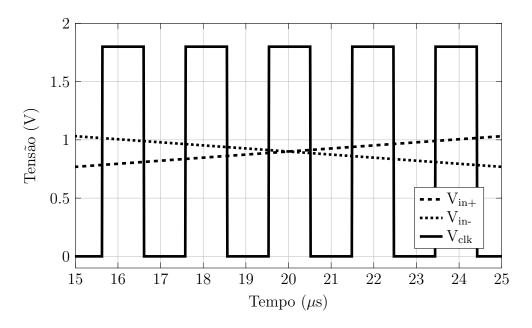

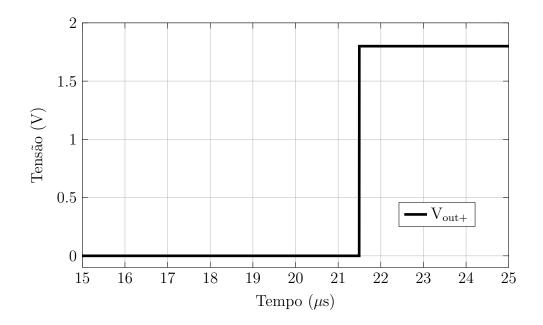

|              |       | 7.1.2   | Quantizador                                                 | 67 |

|              |       | 7.1.3   | Amplificador Operacional de Transcondutância                | 69 |

|              |       | 7.1.4   | Modulador Sigma-Delta Pseudo-Paralelo                       | 71 |

|              | 7.2   | Simul   | ações em Nível de Leiaute                                   | 72 |

|              |       | 7.2.1   | Gerador de Fases do Relógio                                 | 72 |

|              |       | 7.2.2   | Quantizador                                                 | 73 |

|              |       | 7.2.3   | Amplificador Operacional de Transcondutância                | 73 |

|              |       | 7.2.4   | Modulador Sigma-Delta Pseudo-Paralelo                       | 76 |

|              |       | 7.2.5   | Comparação com Outros Trabalhos                             | 79 |

| 8            | Cor   | ıclusõe | es es                                                       | 81 |

|              | 8.1   | Traba   | lhos Futuros                                                | 82 |

| $\mathbf{R}$ | eferê | ncias l | Bibliográficas                                              | 83 |

# Lista de Figuras

| 1.1 | Medidor de energia com função ampère hora                                 | 4  |

|-----|---------------------------------------------------------------------------|----|

| 1.2 | Medidor de energia com função volt-hora                                   | 5  |

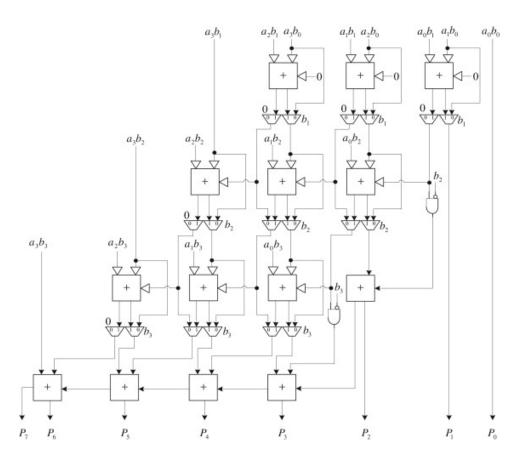

| 2.1 | (a) Produtos parciais de uma multiplicação 4x4 e (b) Multiplicador        |    |

|     | tradicional                                                               | 9  |

| 2.2 | Estrutura da célula de adição                                             | 10 |

| 2.3 | Um multiplicador 4x4 com circuito de desvio                               | 10 |

| 2.4 | Leiaute do multiplicador 16x16 de baixo consumo de energia                | 12 |

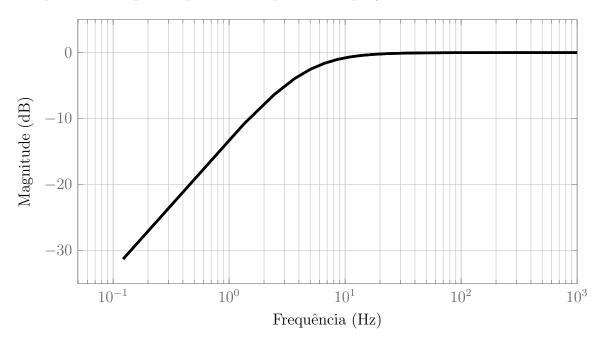

| 3.1 | Resposta em frequência do filtro passa-altas                              | 14 |

| 3.2 | Resposta ao degrau do filtro passa-altas com baixo consumo de energia.    | 15 |

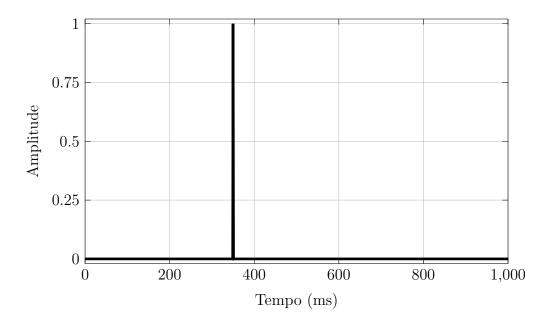

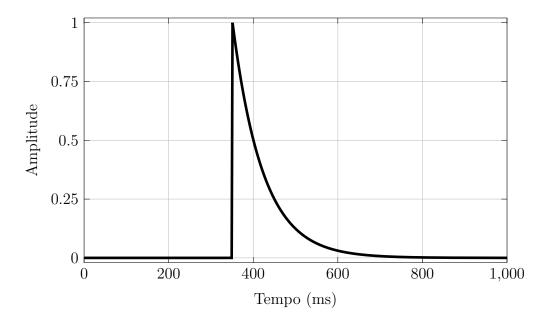

| 3.3 | Resposta ao impulso do filtro passa-altas com baixo consumo de energia.   | 15 |

| 3.4 | Leiaute do filtro passa-altas com baixo consumo de energia                | 16 |

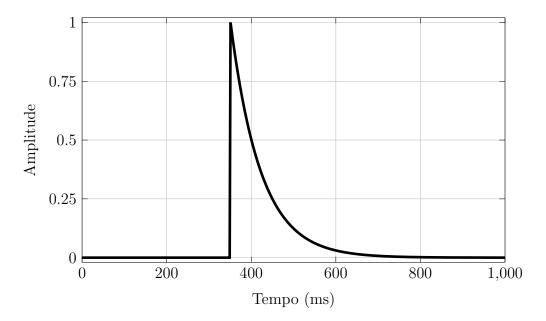

| 3.5 | Resposta em frequência do filtro passa-baixas                             | 17 |

| 3.6 | Resposta ao degrau do filtro passa-baixas com baixo consumo de ener-      |    |

|     | gia                                                                       | 18 |

| 3.7 | Resposta ao impulso do filtro passa-baixas com baixo consumo de           |    |

|     | energia                                                                   | 18 |

| 3.8 | Leiaute do filtro passa-baixas com baixo consumo de energia               | 19 |

| 4.1 | (a) Sinal $X(f)$ (sólido), o ruído moldado (pontilhada) e a resposta em   |    |

|     | frequência da amostragem $H(f)$ (tracejada-ponto); (b) Amostragem         |    |

|     | do sinal $\bar{Y}(f)$                                                     | 22 |

| 4.2 | (a) Sinal $X(f)$ (sólido), (b) o ruído moldado (pontilhada), (c) resposta |    |

|     | em frequência da amostragem $H(f)$ (tracejada-ponto); (d) sinal de        |    |

|     | saída quando a frequência de amostragem $f_s$ é diferente da frequência   |    |

|     | do clock $f'_s$ do SDM                                                    | 23 |

| 4.3 | Diagrama de blocos da implementação de um PSDM de segunda or-             |    |

|     | dem com fator de desenrolamento 2                                         | 24 |

| 4.4 | Representação de um SDM de segunda ordem                                  | 25 |

| 4.5 | Representação de um SDM de segunda ordem                                  | 27 |

| 4.6  | Modelo em Simulink ideal do PSDM de segunda ordem com fator de desenrolamento 2 |

|------|---------------------------------------------------------------------------------|

| 4.7  | Resposta em frequência para o modelo em Simulink ideal do PSDM                  |

|      | de segunda ordem com fator de desenrolamento 2, com os valores de               |

|      | SNR e ENOB                                                                      |

| 4.8  | Histogramas das saídas dos integradores                                         |

| 4.9  | Resposta em frequência para o modelo em Simulink não-ideal do                   |

|      | PSDM de segunda ordem com fator de desenrolamento 2, com os                     |

|      | valores de SNR e ENOB                                                           |

| 5.1  | (a) Resistor ideal a ser simulado, (b) com a técnica de capacitores             |

|      | chaveados                                                                       |

| 5.2  | Resistor simulado com a técnica de capacitores chaveados 3                      |

| 5.3  | (a) Resistor simulado (b) com inversão do sinal                                 |

| 5.4  | (a) Resistor simulado (b) sem inversor do sinal                                 |

| 5.5  | Inversor em nível de transistores                                               |

| 5.6  | Porta lógica NOR em nível de transistores                                       |

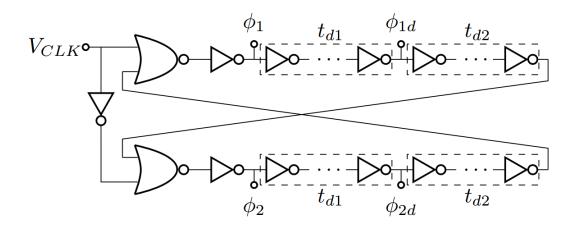

| 5.7  | Gerador de fases do relógio                                                     |

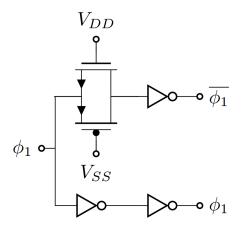

| 5.8  | Geração dos sinais complementares para as chaves                                |

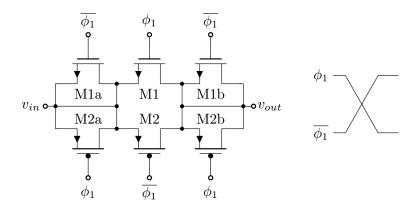

| 5.9  | Chave de transmissão CMOS                                                       |

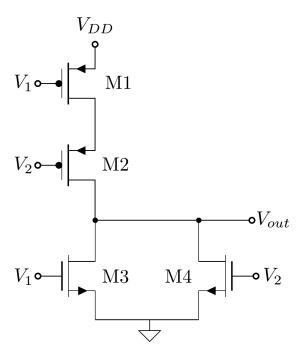

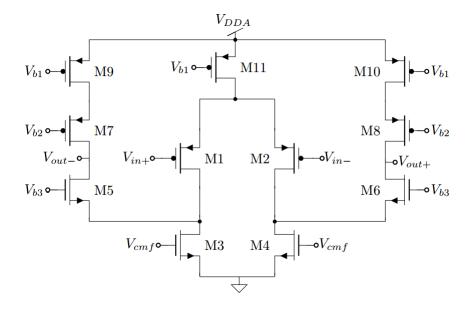

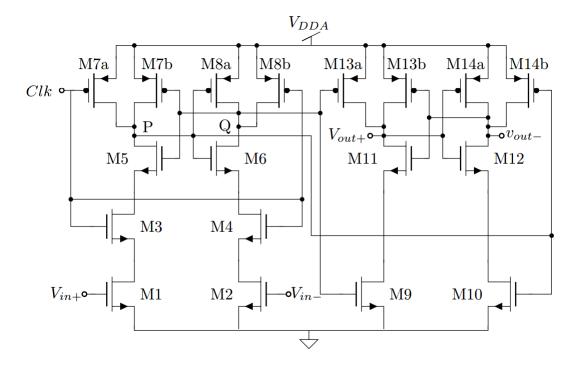

| 5.10 | OTA cascode dobrado                                                             |

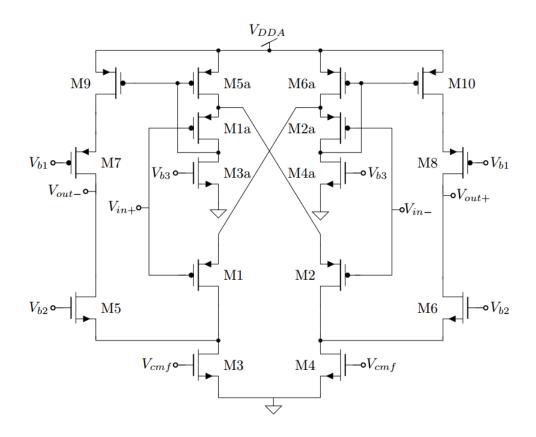

| 5.11 | OTA cascode dobrado com polarização adaptativa [28] 4                           |

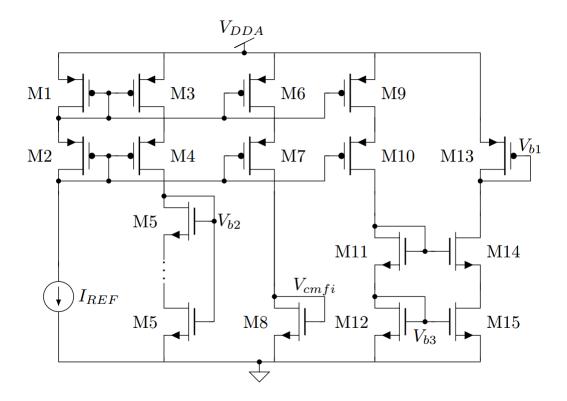

| 5.12 | Circuito de polarização do OTA [28]                                             |

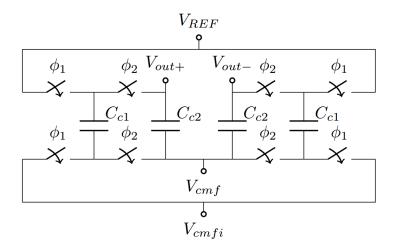

| 5.13 | Circuito de controle da tensão de modo comum do amplificador ope-               |

|      | racional                                                                        |

| 5.14 | Circuito quantizador                                                            |

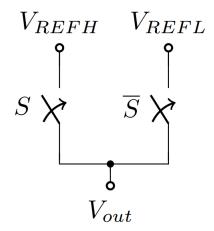

| 5.15 | Circuito conversor digital para analógico de 1 bit                              |

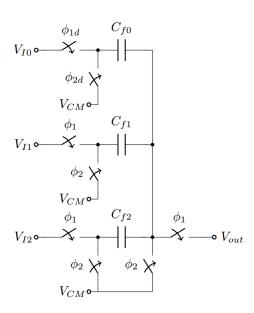

|      | Circuito somador para a saída $V_{out}$                                         |

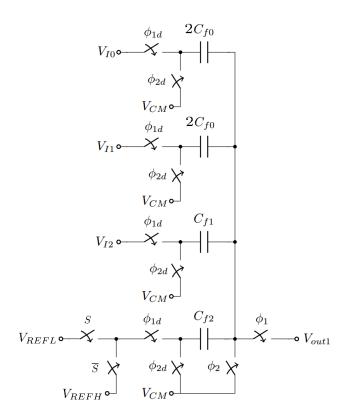

|      | Circuito somador para a saída $V_{out1}$                                        |

| 5.18 | Circuito completo do PSDM                                                       |

| 6.1  | Leiaute do circuito inversor                                                    |

| 6.2  | Leiaute do circuito NOR                                                         |

| 6.3  | Leiaute do circuito gerador de fases do relógio                                 |

| 6.4  | Leiaute da chave CMOS                                                           |

| 6.5  | Leiaute do MUX 2x1                                                              |

| 6.6  | Leiaute do capacitor unitário de 220 $f$ F                                      |

| 6.7  | Arranjo da matriz em centróide comum                                            |

| 6.8  | Leiaute da matriz de capacitores do circuito de controle da tensão              |

|      | modo comum                                                                      |

| 6.9  | Arranjo da matriz do primeiro integrador                                             | 57 |

|------|--------------------------------------------------------------------------------------|----|

| 6.10 | Leiaute da matriz de capacitores do primeiro integrador                              | 58 |

| 6.11 | Arranjo da matriz do segundo integrador                                              | 59 |

| 6.12 | Leiaute da matriz de capacitores do segundo integrador. $\ \ldots \ \ldots \ \ldots$ | 59 |

| 6.13 | Arranjo da matriz do primeiro somador de saída                                       | 60 |

| 6.14 | Leiaute da matriz de capacitores do primeiro somador de saída. $\ . \ . \ .$         | 61 |

| 6.15 | Leiaute da matriz de capacitores do segundo somador de saída                         | 61 |

| 6.16 | Casamento em cross-quad                                                              | 62 |

| 6.17 | Leiaute do amplificador operacional de transcondutância                              | 63 |

| 6.18 | Leiaute do quantizador                                                               | 64 |

| 6.19 | Leiaute final do modulador sigma-delta pseudo-paralelo.                              | 65 |

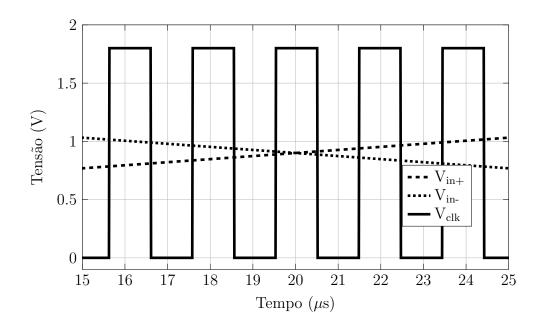

| 7.1  | Simulação do circuito esquemático do gerador de fases do relógio                     | 67 |

| 7.2  | Entradas do quantizador para simulação do circuito esquemático                       | 68 |

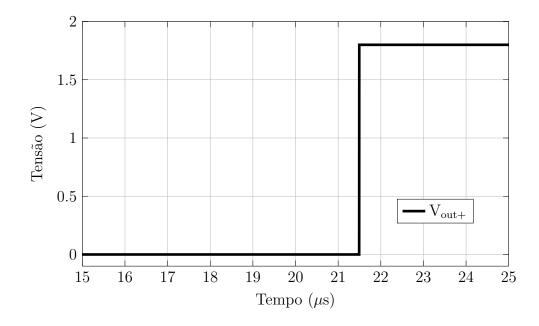

| 7.3  | Saída do quantizador para a simulação do circuito esquemático                        | 68 |

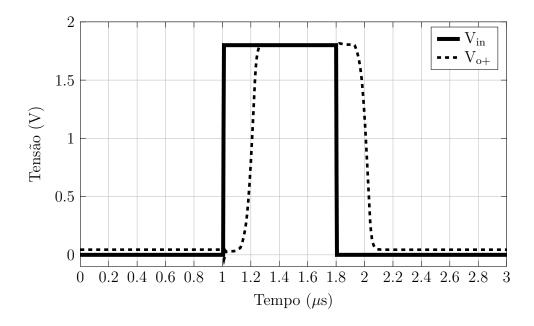

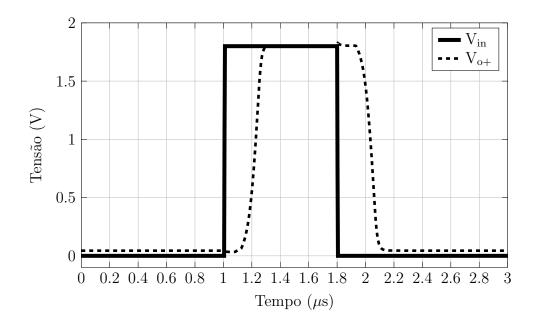

| 7.4  | Resposta ao pulso do circuito esquemático do OTA                                     |    |

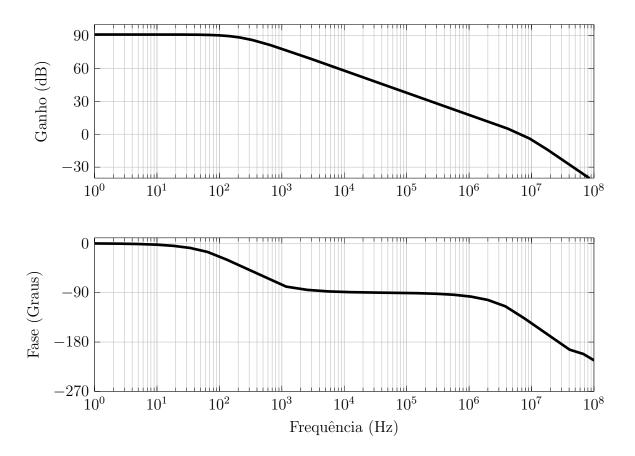

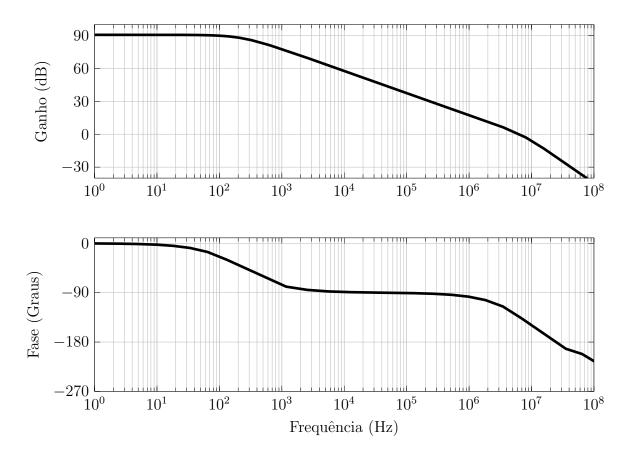

| 7.5  | Resposta em frequência do circuito esquemático do OTA                                |    |

| 7.6  | Resposta em frequência do circuito esquemático do PSDM                               |    |

| 7.7  | Simulação do circuito extraído do gerador de fases do relógio                        |    |

| 7.8  | Entradas do quantizador para simulação do circuito extraído                          |    |

| 7.9  | Saída do quantizador para a simulação do circuito extraído                           |    |

| 7.10 | Resposta ao pulso do circuito extraído do OTA                                        |    |

|      | Resposta em frequência do circuito extraído do OTA                                   |    |

|      | Resposta em frequência do circuito extraído do PSDM                                  |    |

|      | Simulações de Monte Carlo do circuito extraído do PSDM                               | 77 |

|      | Simulações de <i>corners</i> do circuito extraído do PSDM                            | 78 |

| 1.14 |                                                                                      | 10 |

# Lista de Tabelas

| 1.1 | Medidores de energia disponíveis no mercado                                       | 3  |

|-----|-----------------------------------------------------------------------------------|----|

| 2.1 | Comparação entre área ocupada e consumo de energia entre os multiplicadores       | 11 |

| 3.1 | Comparação entre área ocupada e consumo de energia entre os filtros passa-altas.  | 16 |

| 3.2 | Comparação entre área ocupada e consumo de energia entre os filtros passa-baixas. | 18 |

| 4.1 | Coeficientes para obtenção do melhor SNR do modulador                             | 27 |

| 4.2 | Parâmetros de simulação                                                           | 28 |

| 4.3 | Especificações do amplificador                                                    | 30 |

| 5.1 | Dimensionamento dos transistores utilizados nos circuitos digitais                | 36 |

| 5.2 | Dimensão dos transistores da chave CMOS                                           | 39 |

| 5.3 | Dimensionamento dos transistores do OTA cascode dobrado com po-                   |    |

|     | larização adaptativa [28]                                                         | 42 |

| 5.4 | Dimensionamento dos transistores do circuito de polarização do am-                |    |

|     | plificador operacional [28]                                                       | 43 |

| 5.5 | Valores dos capacitores do circuito de controle da tensão de modo                 |    |

|     | comum do amplificador operacional [28]                                            | 44 |

| 5.6 | Dimensionamento dos transistores do quantizador                                   | 45 |

| 5.7 | Valores das tensões de referência do DAC                                          | 46 |

| 5.8 | Valores dos capacitores dos circuitos somadores de saída                          | 47 |

| 5.9 | Valores dos capacitores do PSDM                                                   | 50 |

| 6.1 | Valores dos capacitores utilizados no primeiro integrador                         | 57 |

| 6.2 | Valores dos capacitores utilizados no segundo integrador                          | 58 |

| 6.3 | Valores dos capacitores utilizados no primeiro somador de saída                   | 60 |

| 7.1 | Resultados da simulação do circuito esquemático do quantizador                    | 69 |

| 7.2 | Resultados da simulação do circuito esquemático do OTA                            | 71 |

| 7.3  | Resultados da simulação do circuito esquemático do PSDM             | 71 |

|------|---------------------------------------------------------------------|----|

| 7.4  | Resultados da simulação do circuito extraído do quantizador         | 74 |

| 7.5  | Resultados da simulação do circuito extraído do amplificador opera- |    |

|      | cional                                                              | 76 |

| 7.6  | Resultados da simulação do circuito extraído do PSDM                | 77 |

| 7.7  | Resultados das simulações de Monte Carlo do circuito extraído do    |    |

|      | PSDM                                                                | 78 |

| 7.8  | Resultados das simulações de corners do circuito extraído do PSDM.  | 79 |

| 7.9  | Comparação do PSDM com outros circuitos integrados                  | 80 |

| 7.10 | Comparação do PSDM com outros circuitos integrados. (continuação)   | 80 |

### Lista de Abreviaturas

ADC Analog-to-Digital Converter, p. 6

AMS Austria Micro Systems, p. 2

APS Accelerated Parallel Simulator, p. 66

CMOS Complementary Metal Oxide Semiconductor, p. 1

DAC Digital to Analog Converter, p. 26

EMG Electromyography, p. 79

ENG Electroneurogram, p. 79

ENOB Effective Number Of Bits, p. 28

FIR Finite Impulse Response, p. 13

FOM Figure of Merit, p. 71

GBW Gain-bandwidth product, p. 21

HPF High Pass Filter, p. 5

IIR Infinite Impulse Response, p. 13

LPF Low Pass Filter, p. 5

LSB Least significant bit, p. 78

NMOS N-channel Metal-Oxide-Semiconductor, p. 36

OTA Operational Transcondutance Amplifier, p. 21

PMOS P-channel Metal-Oxide-Semiconductor, p. 36

PSDM Pseudo-Parallel Sigma Delta Modulation, p. 21

PSD Power Spectral Density, p. 28

SDM Sigma Delta Modulator, p. 2

SNR Signal-to-Noise Ratio, p. 6

SR Slew Rate, p. 21

TCAM Transformador de Corrente Auto-Monitorado, p. 3

TC Transformador de Corrente, p. 3

TPAM Transformador de Potencial Auto-Monitorado, p. 4

## Capítulo 1

# Introdução

Medições de qualquer natureza são realizadas a partir de instrumentos que são projetados para atender a determinadas especificações, sendo tais instrumentos responsáveis pela coleta de informações sobre a grandeza que está sendo medida, e por organizar, interpretar e processar essas informações, seja de forma analógica ou digital.

A evolução da tecnologia CMOS (Complementary Metal Oxide Semiconcuctor), permitiu a presença de sistemas eletrônicos em muitos aspectos do dia a dia, como em carros, comunicações, medicina, equipamentos de medição, etc. O avanço das técnicas de fabricação de circuitos integrados, em especial a de CMOS, tem possibilitado aos projetistas inserir cada vez mais funcionalidades a esses dispositivos.

Essa evolução permitiu que a velocidade dos circuitos digitais fosse incrementada possibilitando uma maior frequência de operação. Além disso, a tensão de alimentação foi diminuída para manter campos elétricos moderados dentro do dispositivo, evitando assim correntes de fuga elevadas. Consequentemente o consumo de energia dos circuitos digitais foi diminuído.

O desenvolvimento rápido das tecnologias de circuitos integrados e a disponibilidade de circuitos conversores analógico/digital e microprocessadores têm contribuído para o progresso rápido das técnicas usadas para a medição e, consequentemente, para a melhoria de uma forma geral do desempenho do sistema de medição.

Neste trabalho, faremos algumas considerações sobre os circuitos a serem desenvolvidos para aplicá-los a um medidor de energia elétrica. Começando com o estudo sobre metodologias de redução do consumo de energia aplicadas em diferentes multiplicadores que têm sido propostos na literatura e são classificados em multiplicadores baseados em árvores [1] e multiplicadores baseados em matrizes [2]. A vantagem do multiplicador baseado em árvore está na velocidade atingida, já os multiplicadores baseados em matrizes tem o seu leiaute mais simples. No entanto, o multiplicador baseado em matrizes consome potencialmente mais energia do que a

arquitetura baseada em árvore [3]. A razão é que os somadores adicionais incorporados ao multiplicador baseado em árvores absorvem a comutação espúria e, portanto, reduzem o consumo de energia [4]. Porém, o leiaute do multiplicador baseado em árvore tende a ser complicado e induz mais capacitâncias parasitas. Além disso, é limitado a um comprimento de operando mais curto, menor que 16 bits [5]. O multiplicador com operandos com tamanho maior ou igual a 16 pode ser implementado pelo multiplicador Wallace usando a codificação de Booth. Mas essa adaptação deixa os multiplicadores baseados em árvore ainda mais complexos, por isso a arquitetura baseada em matriz é utilizada para o desenvolvimento do multiplicador. Essa arquitetura alia alta velocidade de execução e taxa de transferência, no entanto, o aumento da carga capacitiva e o tamanho dos operandos binários resultam em uma dissipação de potência muito grande [6]. As transições em circuitos digitais são responsáveis pela dissipação de energia devido à carga e descarga de capacitores. Uma técnica utilizada em multiplicadores digitais é focar na diminuição do número de chaveamentos para reduzir a dissipação de energia. Em [7], foi proposto um multiplicador que adiciona hardware para evitar cálculos redundantes e desativar as unidades somadoras cujo produto parcial é igual a zero. Essa técnica é essencial para a redução do consumo de energia do multiplicador digital e também dos filtros digitais aqui desenvolvidos.

E por fim, demonstraremos o modulador sigma-delta (SDM) e daremos explicações a respeito do funcionamento da nova topologia que será utilizada para se reduzir o consumo de energia. Em [8] e [9] o desenvolvimento de moduladores altamente lineares com grandes larguras de banda de entrada é incentivado. Nessas topologias os requisitos de velocidade de processamento de sinais são reduzidos, devido ao processamento paralelo.

Uma abordagem alternativa que evita o uso de múltiplos SDMs, também baseada em processamento paralelo, é descrita em [10]. Esse modulador é um componente essencial no desenvolvimento de um conversor analógico digital, que por sua vez pode ser usado para fornecer os sinais necessários ao funcionamento do medidor. Todos os componentes foram projetados para a tecnologia CMOS 0,18  $\mu$ m da AMS (Austria Micro Systems) e operação utilizando tensão de alimentação de 1,8V visando o baixo consumo de energia.

#### 1.1 Motivação

Nos sistemas de medição de energia elétrica, os transformadores para instrumentos, que são equipamentos que também fazem parte do sistema de medição, não fornecem informações de seu desempenho sem a realização de ensaios por meio de instrumentos externos. E essas verificações não são permanentes, nem obtêm informações em

tempo real do desempenho no campo.

Devido a esses problemas, nos últimos anos o conceito de medidores de energia (Smart Meter) e redes inteligentes (Smart Grids) tem sido bastante difundido, com o objetivo de assegurar uma maior capacidade do sistema de medição de automaticamente detectar, analisar e restaurar falhas, dessa forma fornecendo energia com qualidade e eficiência [11], [12].

Com o objetivo de aprimorar o desenvolvimento de medidores de energia inteligentes, um estudo comparativo das funcionalidades de alguns circuitos integrados de medição de energia foi realizado em [13]. Com base nesse estudo, em [14] foi proposto um medidor de energia inteligente que usa os recursos do CI ADE7758 para o desenvolvimento de um sistema que incorpora recursos de monitoração de parâmetros de energia de equipamentos e executa funções como monitoramento de energia em tempo real, fator de potência e alertas contra sobretensão e sobrecorrente. Na Tabela 1.1 são listados alguns medidores de energia que estão disponíveis no mercado e suas características.

Tabela 1.1: Medidores de energia disponíveis no mercado.

| Medidor  | $V_{DD}$ (V) | $V_{REF}$ (V) | ADC Bits | $f_S$ (Hz) | BW (Hz)   |

|----------|--------------|---------------|----------|------------|-----------|

| ADE7753  | 5,00         | 2,40          | 24       | 894,0 k    | 40-2,0 k  |

| ADE7758  | 5,00         | 2,40          | 24       | 894,0  k   | 40-2,0  k |

| ATT7022B | 5,00         | 2,40          | 16       | 3,2 k      | 40-2,0  k |

| MCP3910  | 2,7-3,60     | 1,20          | 24       | 1000,0  k  | 40-2,0  k |

| ATM90E26 | 3-3,60       | 1,26          | 16       | 8,0  k     | 40-2,0  k |

| STPM34   | 2,95-3,65    | 1,18          | 24       | 7,8 k      | 0-3,6 k   |

Como pode ser observado, em CIs de medição de energia elétrica a largura de banda do sinal de entrada varia tipicamente de 40 Hz a 2 kHz. Esses valores são determinados pelas especificações da norma IEC-61036, que exige mais de 20 harmônicos, ampla faixa dinâmica e precisão de medição de 0,5%.

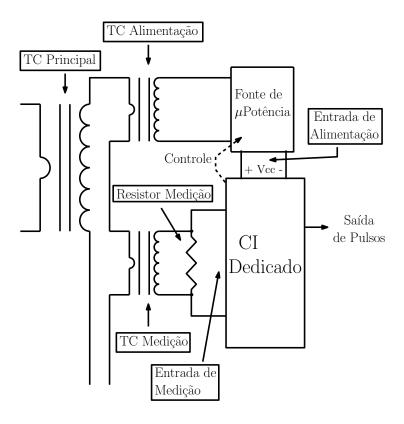

Com base nas especificações da norma IEC-61036, apresenta-se o diagrama de blocos de uma implementação TCAM (Transformador de Corrente Auto-Monitorado) com medição de corrente apenas no secundário do TC (Transformador de Corrente) [15]. Esta implementação tem como base a aplicação de circuitos integrados de baixo consumo de energia. Para o TCAM, a função do CI é contabilizar a grandeza Ampère-hora, utilizando uma fonte de micropotência para alimentação que deve estar baseada em uma parcela ínfima da corrente elétrica que circula no circuito externo. A implementação sugerida usa um TC para alimentação e um TC para medição.

Figura 1.1: Medidor de energia com função ampère hora.

O TC de alimentação fornece uma corrente para uma microfonte de potência que converte em tensão contínua para a alimentação do circuito integrado. O TC de medição transmite o sinal de corrente a ser medido, que é então convertido para tensão por um resistor como mostrado na Figura 1.1.

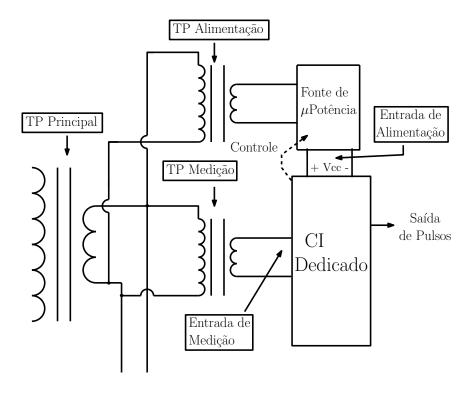

No caso do TPAM (Transformador de Potencial Auto-Monitorado), a preocupação com baixo consumo persiste, com o objetivo de manter-se o menor consumo possível em volt-ampère no secundário do transformador de potencial [15]. Na Figura 1.2 apresenta-se o diagrama de blocos de uma implementação do TPAM, tendo como base a aplicação da tecnologia de circuitos integrados utilizando técnicas de baixo consumo de energia.

Figura 1.2: Medidor de energia com função volt-hora.

Os circuitos integrados que foram desenvolvidos nesta tese podem ser utilizados em uma combinação dessas duas técnicas de medição, para se obter a medida precisa de watt-hora. Nessa implementação o trabalho de medição é realizado por um circuito integrado de baixíssimo consumo, sendo alimentado por uma fonte de micropotência que retirará energia apenas do secundário do transformador para a sua alimentação.

#### 1.2 Objetivos

Essa tese de doutorado tem como objetivo apresentar circuitos digitais e mistos de baixo consumo de energia que foram desenvolvidos e que podem ser utilizados por um medidor de energia, como os que foram apresentados na Seção 1.1. Dentre esses circuitos temos:

- Um multiplicador digital de baixo consumo que realiza a multiplicação entre os sinais digitais de tensão e corrente medidos no transformador, gerando assim a medição de watt-hora;

- Um filtro digital passa-altas HPF (High Pass Filter) de baixo consumo de energia que remove uma componente DC que possa surgir no sinal que será medido;

- Um filtro digital passa-baixas LPF (Low Pass Filter) de baixo consumo de energia que é responsável pela extração da informação de potência real (componente DC) do sinal de potência instantânea;

• Um modulador  $\Sigma\Delta$  de baixo consumo de energia, que possua uma elevada razão sinal ruído SNR (Signal-to-Noise Ratio) de modo a se alcançar 16 bits na saída de um conversor analógico para digital ADC (Analog-to-Digital Converter) para um sinal que possua uma faixa de frequência entre 40Hz e 2kHz;

#### 1.3 Estrutura do Texto

- O Capítulo 2 introduz o conceito do multiplicador de baixo consumo de energia, e como esse circuito utiliza a técnica de desvio para evitar o acionamento de determinados componentes da multiplicação que geram valores redundantes.

- O Capítulo 3 descreve os projetos dos filtros digitais passa-altas e passa-baixas utilizados na estrutura do circuito de medição de energia.

- O Capítulo 4 expõe o conceito do modulador  $\Sigma\Delta$  pseudo paralelo e detalha como essa técnica pode ser utilizada para a redução do consumo de energia.

- O Capitulo 5 apresenta o desenvolvimento dos componentes em nível de transistores do modulador  $\Sigma\Delta$  pseudo paralelo.

- O Capitulo 6 apresenta o desenvolvimento dos componentes em nível de leiaute do modulador  $\Sigma\Delta$  pseudo paralelo.

- O Capitulo 7 demonstra os resultados das simulações e das medições que comprovam o funcionamento dos circuitos desenvolvidos.

- O Capitulo 8 finaliza com as conclusões e perspectivas para trabalhos futuros.

## Capítulo 2

## Multiplicador com Baixo Consumo

Com as exigências cada vez mais rigorosas sobre o espaço da bateria e seu peso em dispositivos portáteis, circuitos eficazes no consumo de energia são necessários. A preocupação principal é estender as horas de funcionamento sem mudar a bateria do dispositivo. Embora o avanço da tecnologia melhore o uso da bateria para operar por mais horas, operações complexas nos dispositivos ainda são críticas para projetos de baixo consumo de energia. Um projeto de baixo consumo pode ser alcançado através de melhorias no sistema, na lógica, na escolha da tecnologia e em melhorias no circuito.

A economia de energia pode ser significativa se o projeto de baixo consumo for planejado desde o nível do sistema, otimizando a lógica do circuito para este fim. À medida que os processos de fabricação diminuem de tamanho, o consumo de energia pode ser reduzido ao mesmo tempo. Muitos esforços para atingir baixas exigências de energia a nível de circuito podem ser vistos na literatura [3], [4], [5], [6], [7]. Esses esforços concentram-se na redução da tensão de alimentação, ajustes na tensão de limiar, estratégias de desligamento de partes do circuito e estilo de lógica. Estas opções podem ser escolhidas em nível de circuito e topologia para implementar diferentes funções aritméticas. Por exemplo, para desenvolver um somador, pode ser adotado ripple-carry, carry-save ou carry look-ahead. Ao escolher uma dessas arquiteturas, o baixo consumo de energia pode ser alcançado em detrimento de outras especificações, como velocidade ou área de chip.

Multiplicadores são os blocos de construção de processadores de sinais digitais. Além de somadores, multiplicadores digitais são as unidades funcionais aritméticas mais críticas em muitas aplicações em processamento digital de sinais, por exemplo, Transformada de Fourier, Transformada discreta de cossenos, filtragem, etc.

#### 2.1 Técnica de Desvio

Multiplicadores convencionais podem ser classificados em iterativos e baseados em matrizes. O multiplicador iterativo pode realizar a multiplicação através de uma série de operações de deslocamento e adição. Uma vez que pode reutilizar o mesmo hardware para realizar a multiplicação, ocupa menos área do que outros multiplicação e não pode ser realizado em uma estrutura de pipeline. Por outro lado, multiplicadores baseados em matrizes são mais utilizados devido à sua estrutura ser organizada por vários estágios de somadores e portas lógicas 'E'. São gerados todos os produtos parciais após apenas um atraso da porta lógica 'E' e após isso todos os produtos parciais são somados sequencialmente. A vantagem desta estrutura é que a disposição dos somadores facilita o leiaute e também permite ser utilizado em um estrutura paralela. No entanto, ocupa mais área e componentes do que o multiplicador iterativo.

Multiplicadores baseados em matrizes e paralelos são utilizados, devido à sua alta velocidade de execução e taxa de transferência. No entanto, o aumento da carga capacitiva e o tamanho dos operandos binários resultam em uma dissipação de potência muito grande [6]. Em circuitos CMOS estáticos, a atividade de transição é responsável pelo total da dissipação de energia devido à carga e descarga de capacitores. Dada a capacidade de carga média (C), a tensão de alimentação (V), e o número (a) de transistores consumindo energia por operação, a dissipação de energia média [7] de um multiplicador CMOS digital pode ser expressa por:

$$E = a \cdot C \cdot V^2 \tag{2.1}$$

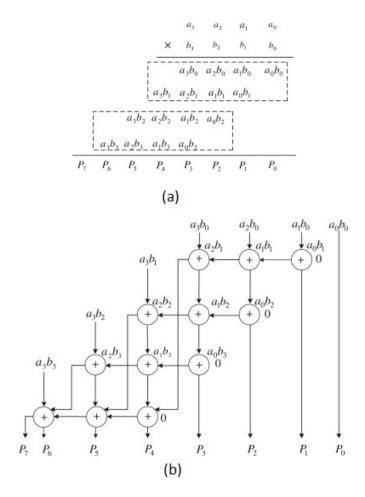

Uma técnica utilizada em multiplicadores digitais é reduzir o número de transições minimizando o chaveamento para reduzir a dissipação de energia. Um multiplicador usando essa técnica foi proposto em [7], a abordagem proposta é adicionar hardware para evitar cálculos redundantes, desativando as unidades somadoras cujo produto parcial torna-se zero. Este método depende de uma lógica de decisão para identificar que um produto parcial é igual a zero para ignorar ou desligar os somadores de uma linha. Na Figura 2.1 é mostrado o exemplo de uma multiplicação 4x4.

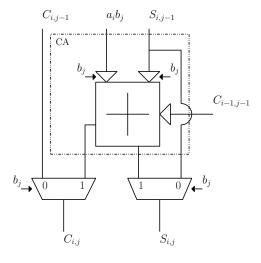

Para eliminar as transições de sinal redundantes, os somadores em que o produto parcial é zero são desabilitados, enquanto o produto parcial das linhas de somadores anterior é deslocado e desviado para a próxima linha de somadores. A estrutura da célula de adição utilizada para realizar essa operação pode ser visualizada na Figura 2.2. Nesta estrutura, dois multiplexadores foram adicionados nas saídas do somador

Figura 2.1: (a) Produtos parciais de uma multiplicação 4x4 e (b) Multiplicador tradicional.

completo para transmitir a entrada do carry e a soma da adição anterior para as saídas, quando o bit correspondente  $b_j$  é zero. Os buffers tri-state, colocados nas entradas da célula de adição, desativam os sinais de transição nessas células fazendo o desvio. A saída de bit do carry  $C_{i,j}$  é passada para baixo.

A Figura 2.3 mostra o esquema de implementação desse multiplicador com baixo consumo para um exemplo de multiplicação 4x4. Em comparação a estrutura tradicional de um multiplicador 4x4 mostrado na Figura 2.1 (b), pode-se notar que o esquema inclui modificações na célula de adição, com um circuito de desvio que é utilizado para desabilitar transições desnecessárias e para desviar as entradas para as saídas quando o produto parcial correspondente é igual à zero.

Para a aplicação do medidor de energia foi definido que o conversor A/D sigmadelta terá uma resolução de 16 bits, e com isso em mente para se obter o valor de energia medido em Watts é necessária a multiplicação dos valores medidos de tensão (V) e corrente (I) obtidos no transformador. Assim se faz necessário um multiplicador de baixo consumo de energia de 16x16, para isso basta se expandir o

Figura 2.2: Estrutura da célula de adição.

Figura 2.3: Um multiplicador 4x4 com circuito de desvio.

conceito explicado anteriormente e exibido na Figura 2.3.

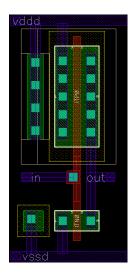

#### 2.2 Circuito Multiplicador 16x16

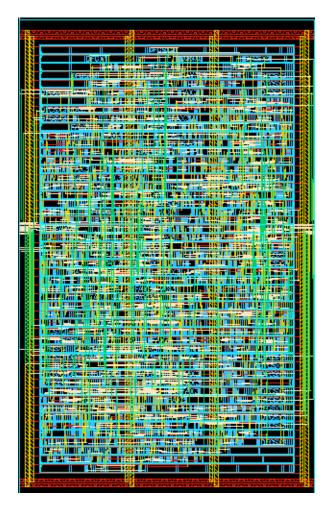

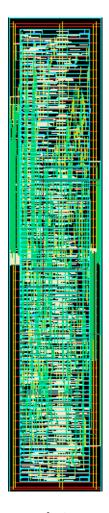

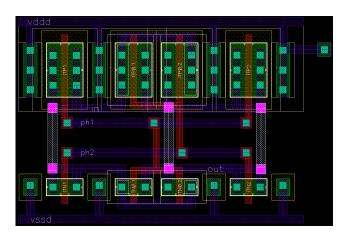

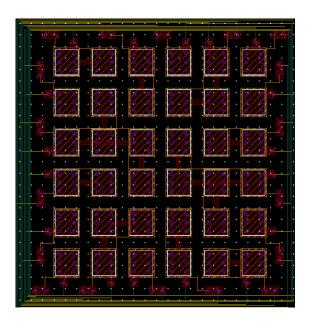

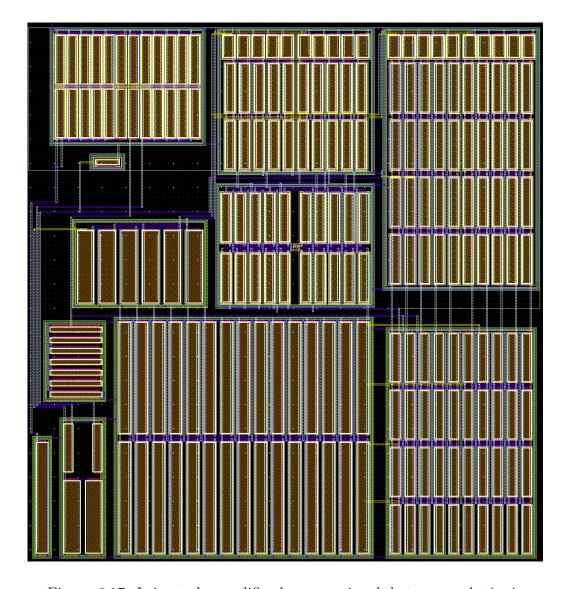

Nesta seção, é apresentada a avaliação de desempenho do multiplicador proposto juntamente com a comparação com um multiplicador tradicional. Foi avaliado o consumo de energia e área de leiaute, utilizando as bibliotecas digitais fornecidas pela tecnologia AMS  $0.18~\mu m$  e com uma tensão de alimentação de 1.8~V. O circuito do multiplicador de baixo consumo de energia de 16x16 foi desenvolvido utilizando a linguagem de descrição de hardware Verilog, com essa linguagem é possível definir o funcionamento do circuito e também fazer testes para verificar o seu funcionamento correto. Com o auxílio das ferramentas de desenvolvimento de circuitos integrados digitais fornecidas pela Cadence, RTL Compiler e Encounter, foram feitas simulações para estimar o consumo e a área que seria ocupada pelo multiplicador. O circuito obtido em nível de leiaute pode ser observado na Figura 2.4.

Para efeito de comparação também foi construído um multiplicador sem utilizar técnicas de diminuição de consumo de energia com o auxílio das ferramentas de sintetização de Verilog disponíveis no conjunto de ferramentas da Cadence. Com essas ferramentas foi possível medir o consumo de energia de cada uma das abordagens, com o intuito de se obter o real nível de economia de energia e quais as diferenças para o circuito tradicional, que podem ser observados abaixo.

Tabela 2.1: Comparação entre área ocupada e consumo de energia entre os multiplicadores.

|                       | Multiplicador Tradicional | Multiplicador com Baixo Consumo |

|-----------------------|---------------------------|---------------------------------|

| Quantidade de células | 500                       | 1682                            |

| Área Ocupada          | $13600 \ \mu m^2$         | $47600 \ \mu \text{m}^2$        |

| Consumo de Energia    | $736~\mu\mathrm{W}$       | $437 \mu W$                     |

Como pode ser observado na Tabela 2.1, o multiplicador de baixo consumo aqui desenvolvido apresentou uma melhora significativa no consumo de energia se comparado ao multiplicador tradicional. No entanto, cabe ressaltar que esse ganho de 40% no consumo veio com o aumento da área. O multiplicador tradicional é 3,36 vezes menor que o multiplicador de baixo consumo. Mas como a aplicação do medidor de energia solicita um baixo consumo de energia para que a medição não seja alterada, esse aumento na área ocupada se faz necessário.

Figura 2.4: Leiaute do multiplicador 16x16 de baixo consumo de energia.

## Capítulo 3

### Filtros Digitais

Em um sistema, a função de um filtro é remover partes não desejadas do sinal, como o ruído, ou extrair partes úteis do sinal, como determinadas componentes de frequência que estão dentro da faixa de passagem. Essa é uma área de muito interesse em sistemas de energia elétrica devido à possibilidade de automatização dos cálculos e realização "on-line" da monitoração usando processadores digitais. Os principais campos de aplicação são medição, proteção e controle digital de processos, avaliação da qualidade de energia elétrica, cálculo de indicadores de qualidade, etc [16].

Os filtros podem ser classificados em analógicos e digitais. Os filtros analógicos estão relacionados com o sinal analógico em sua entrada que é contínuo no tempo e os filtros digitais têm entrada digital que é discreta no tempo. Para o projeto do medidor de energia de baixo consumo serão utilizados filtros digitais, pois os sinais de entrada já foram convertidos de analógicos para digitais por um conversor sigma-delta.

O filtro digital IIR (*Infinite Impulse Response*) é uma das ferramentas mais utilizadas quando se é preciso realizar um processamento digital do sinal, pois a ordem de um filtro FIR (*Finite Impulse Response*) é normalmente mais elevada para a mesma especificação. Isso tende a um uso maior de estruturas de memória e aritméticas, o que em termos de custo de implementação em um circuito integrado acaba sendo superior a de um filtro IIR que satisfaz as mesmas respostas em magnitude [17]. Devido a essa característica foram desenvolvidos para esse trabalho filtros IIR que se utilizam da técnica de redução de consumo descrita no Capítulo 2. Há um grande número de métodos para projetar filtros IIR, um dos métodos mais utilizados é a concepção de filtros digitais com o auxílio do programa MATLAB. Esta metodologia é melhor para a concepção de todos os tipos de filtros como passa-alta, passa-baixa, passa-faixa e rejeita-faixa.

Nas próximas seções serão explicados quais filtros foram utilizados e como foram implementados em circuito integrado.

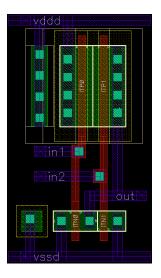

#### 3.1 Filtro Passa-Altas

Um filtro passa-altas permite a passagem de sinais com uma frequência superior a certa frequência de corte e atenua os demais sinais. A atenuação para cada frequência depende do projeto do filtro [18]. O filtro passa-altas tem muitos usos, sendo um deles a remoção da componente CC de um sinal. Nesse circuito de medição, o valor da potência real é extraído da potência instantânea. Então qualquer componente CC presente no valor de tensão e corrente medidos afeta diretamente a medição da potência instantânea e causará erro no cálculo da potência real. Para se remover essa componente CC do sinal de potência instantânea foi desenvolvido um filtro passaaltas que será introduzido logo após a medição de corrente e tensão pelo conversor sigma-delta. Como a filtragem passa-altas introduz um atraso de fase foi inserido o mesmo filtro em cada um dos canais de medição. Como os filtros são chaveados pelo mesmo clock digital, a diferença de fase entre eles é praticamente nula, tendo a frequência da linha de 60 Hz. Para essa remoção, a frequência de corte do filtro é de 4,45 Hz que induz um erro de ganho mínimo na frequência da linha e permite tempo de acomodação suficiente para a aplicação. Na Figura 3.1 se pode observar a resposta em frequência para o filtro passa-altas projetado.

Figura 3.1: Resposta em frequência do filtro passa-altas.

O filtro que possui a resposta em frequência acima é um filtro de primeira ordem que foi projetado com o auxílio do programa Matlab e das ferramentas Cadende, RTL Compiler e Encounter, que permitem a síntese do código em verilog para o leiaute do circuito integrado. Esse filtro possui alguns multiplicadores que se utilizam

da técnica de redução de energia descrita anteriormente.

Nas Figuras 3.2 e 3.3 podem ser vistas as respostas ao degrau e ao impulso do filtro de baixo consumo projetado.

Figura 3.2: Resposta ao degrau do filtro passa-altas com baixo consumo de energia.

Figura 3.3: Resposta ao impulso do filtro passa-altas com baixo consumo de energia.

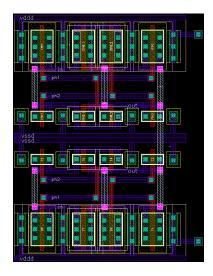

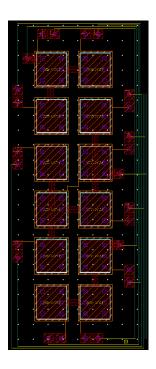

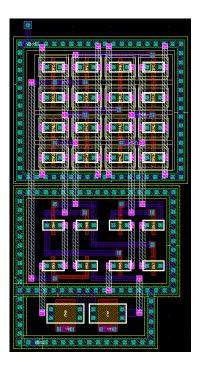

Na Figura 3.4 se pode observar o leiaute desse filtro na tecnologia CMOS 0,18  $\mu m$  da AMS.

Para efeito de comparação um filtro passa-altas com os mesmo requisitos foi desenvolvido sem utilizar a técnica de redução de energia e os resultados podem ser

Figura 3.4: Leiaute do filtro passa-altas com baixo consumo de energia.

comparados na Tabela 3.1.

Tabela 3.1: Comparação entre área ocupada e consumo de energia entre os filtros passa-altas.

|                       | Filtro Passa-Altas Tradicional | Filtro Passa-Altas com Baixo Consumo |

|-----------------------|--------------------------------|--------------------------------------|

| Quantidade de células | 706                            | 983                                  |

| Área Ocupada          | $13200 \ \mu {\rm m}^2$        | $18200 \ \mu { m m}^2$               |

| Consumo de Energia    | $112~\mu\mathrm{W}$            | $95~\mu\mathrm{W}$                   |

Como pode ser observado na Tabela 3.1, novamente o uso da técnica de redução de energia foi eficaz. Houve um consumo cerca de 15% menor que o filtro passa-altas tradicional, mas essa redução no consumo aumentou a área do filtro em 1,4 vezes se comparado ao tradicional. Como o objetivo do medidor é ter um baixo consumo, essa diferença na área não é preocupante.

#### 3.2 Filtro Passa-Baixas

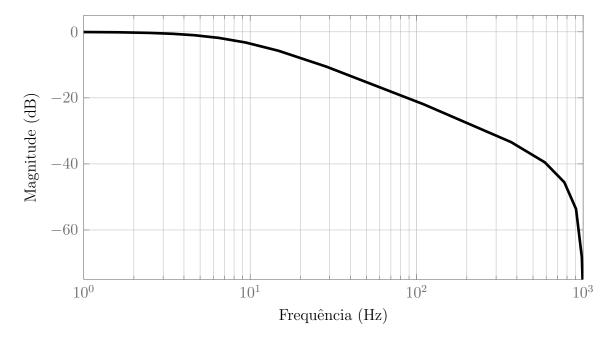

O filtro passa-baixas aqui desenvolvido é um filtro IIR de primeira ordem que extrai a informação de potência real (componente DC) do sinal de potência instantânea. A resposta em frequência deste filtro é apresentada na Figura 3.5.

Figura 3.5: Resposta em frequência do filtro passa-baixas.

Devido ao fato do sinal de potência instantânea possuir componentes harmônicas, e uma vez que o filtro não é ideal, haverá alguma ondulação na saída do filtro passabaixas para as harmônicas da frequência de linha. A frequência de corte do filtro é 8,9 Hz e foi escolhida para extrair a componente DC principal para as frequências de linha mais usadas que são 50 Hz e 60 Hz. Esse filtro possui alguns multiplicadores que se utilizam da técnica de redução de energia descrita anteriormente.

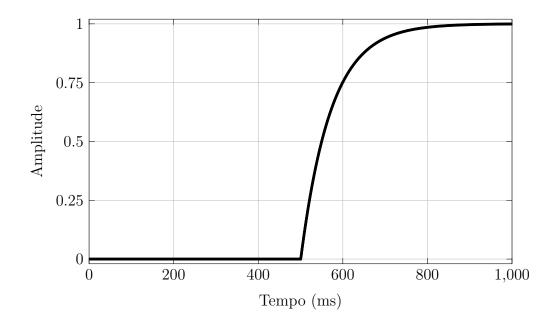

Nas Figuras 3.6 e 3.7, podem ser vistas as respostas ao degrau e ao impulso do filtro de baixo consumo projetado.

Na Figura 3.8 se pode observar o leiaute desse filtro na tecnologia CMOS 0,18  $\mu m$  da AMS.

Para efeito de comparação um filtro passa-baixas com os mesmos requisitos foi desenvolvido sem utilizar a técnica de redução de energia e os resultados podem ser comparados na Tabela 3.2.

Figura 3.6: Resposta ao degrau do filtro passa-baixas com baixo consumo de energia.

Figura 3.7: Resposta ao impulso do filtro passa-baixas com baixo consumo de energia.

Tabela 3.2: Comparação entre área ocupada e consumo de energia entre os filtros passa-baixas.

|                       | Filtro Passa-Baixas Tradicional | Filtro Passa-Baixas com Baixo Consumo |

|-----------------------|---------------------------------|---------------------------------------|

| Quantidade de células | 741                             | 1698                                  |

| Área Ocupada          | $13200 \ \mu m^2$               | $30400 \ \mu \text{m}^2$              |

| Consumo de Energia    | $178~\mu\mathrm{W}$             | $131~\mu\mathrm{W}$                   |

Figura 3.8: Leiaute do filtro passa-baixas com baixo consumo de energia.

Como pode ser observado na Tabela 3.2, novamente o uso da técnica de redução de energia foi eficaz. Houve um consumo cerca de 26% menor que o HPF tradicional, mas essa redução no consumo aumentou a área do filtro em 2,3 vezes se comparado ao tradicional. Como o objetivo do medidor é ter um baixo consumo, essa diferença na área não é preocupante.

### Capítulo 4

# Modulador Sigma-Delta Pseudo-Paralelo

A técnica de sobre-amostragem utilizada nos moduladores sigma-delta (SDMs) permite que esses componentes possuam uma linearidade elevada e essa é a principal razão para a popularidade destes em conversores de dados [19], [20], [21]. Porém, para atingir este grau de linearidade uma alta taxa de sobre-amostragem é necessária, aumentando a necessidade de processamento em alta velocidade, o que eleva o consumo de energia [10].

Algumas aplicações têm incentivado projetistas a desenvolver conversores altamente lineares com grandes larguras de banda de entrada [8], [9]. O uso de moduladores de ordem elevada e razões de sobre-amostragens menores é uma alternativa que tem sido utilizada, mas apresenta como desvantagem a instabilidade de SDMs de ordem mais alta.

O conceito de processamento de sinal multitaxas para reduzir a razão de sobreamostragem tem sido utilizado por muitos trabalhos de pesquisa. Em [22] foi proposto um novo SDM de processamento paralelo que utiliza moduladores interconectados trabalhando em paralelo com cada um funcionando no mesmo clock. Uma arquitetura que faz o uso mais eficiente de área foi proposta em [23] e consiste na combinação de vários SDMs em paralelo, juntamente com pré-processamento analógico do sinal de entrada e pós-processamento digital dos sinais de saída. Uma arquitetura Sigma-Delta entrelaçada no tempo foi usada em [24] para aumentar a largura de banda do conversor com uma menor complexidade de hardware. Em [25] uma transformação de Hadamard foi utilizada para se decompor o espectro de entrada em várias sub-bandas, as quais foram, em seguida, aplicadas em SDMs separados, cujas saídas foram subsequentemente recombinadas.

No trabalho [10], uma abordagem alternativa que evita o uso de múltiplos SDMs, também baseada em processamento paralelo, é descrita. O Modulador Sigma-Delta Pseudo-Paralelo (PSDM) implementa etapas de processamento combinadas e simpli-

ficadas para n clocks sequenciais de um SDM tradicional. Trata-se de um modulador que combina n malhas fechadas que geram n bits por ciclo de clock. A frequência de amostragem mais elevada do PSDM é deslocada para um multiplexador, fazendo a taxa de seleção desse multiplexador ser igual à frequência de amostragem de um SDM tradicional de um único bit. Os outros elementos de processamento do PSDM operam com uma velocidade n vezes menor do que a do SDM de bit único tradicional.

O presente trabalho apresenta o projeto de um PSDM como um estágio de um conversor analógico-digital (ADC) para aplicações de medição de energia elétrica. O modulador foi projetado para a tecnologia AMS 0,18  $\mu$ m e utilizando 1,8 V de tensão de alimentação. O ADC sigma-delta é dividido em dois estágios principais: um PSDM (domínio analógico) e o decimador (domínio digital). Este último consiste num filtro digital e um redutor de frequência que fornece um sinal de frequência limitado com um número específico de bits e uma frequência de amostragem reduzida (tipicamente pela mesma razão que a razão de sobre-amostragem). O PSDM transmite o sinal de entrada modulado para o circuito digital com uma SNR para satisfazer a resolução necessária.

O projeto do sistema de medição descrito neste trabalho funciona em baixas frequências, e seu ADC requer um grande número de bits. Este é o caso de CIs de medição de energia elétrica em que a largura de banda do sinal de entrada varia tipicamente de 40 Hz a 2 kHz. Esses valores são determinados pelas especificações da norma IEC-61036, que exige mais de 20 harmônicos, ampla faixa dinâmica e precisão de medição de 0,5%. Vale ressaltar que o ADC recebe um sinal de amplitude quase constante pois é precedido por um amplificador de ganho programável. Um parâmetro de qualidade importante do CI de medição é baseado no seu baixo consumo de energia, especialmente porque extrai a energia da fonte a ser medida.

Como o principal consumidor de energia estática em um modulador sigma-delta é o amplificador operacional de transcondutância (OTA), pois este requer alto produto ganho-banda (GBW) e rápida taxa de variação da tensão de saída (SR), o projeto deste amplificador usando o consumo mínimo de energia representa um grande desafio.

Neste trabalho, se encontra o desenvolvimento de um modulador sigma-delta baseado na proposta descrita em [10]. No entanto aqui o circuito está sendo projetado para trabalhar com circuitos analógicos, diferente do proposto no artigo [10], que é fundamentalmente digital. A principal contribuição deste trabalho é a concepção de um PSDM que se adapte aos requisitos de aplicação de sistemas de medição de energia elétrica (TCAM e TPAM), com baixo consumo de energia devido à sua característica de redução da taxa de sobre-amostragem.

#### 4.1 PSDM de Baixa Sobre-Amostragem

Esta seção explica o funcionamento da arquitetura PSDM que se utiliza da técnica de baixa sobre-amostragem proposta em [10] que gera na saída do SDM um sinal digital de dois níveis. Para o SDM tradicional, a frequência de amostragem do sinal de entrada e a frequência do clock do SDM são tipicamente iguais.

Supondo que a frequência de amostragem do sinal de entrada é  $f_s$ , enquanto a frequência de clock do SDM é  $f'_s$ , e assumindo que  $f'_s > f_s$  e  $f'_s/f_s$  é um valor inteiro positivo, N. Após N períodos de clock, o SDM processa uma entrada constante.

A frequência  $f'_s$  se refere à frequência de seleção da entrada do multiplexador que é igual à taxa de saída do PSDM. Esta frequência  $f'_s$  também pode ser considerada como a frequência efetiva do PSDM que é igual à frequência de amostragem de um SDM tradicional. A frequência de processamento de todos os elementos de processamento do PSDM é  $f_s$  exceto pela frequência do multiplexador que é  $f'_s$ .

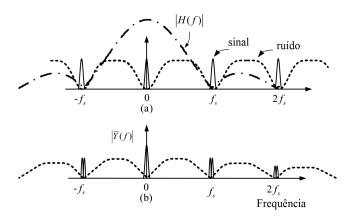

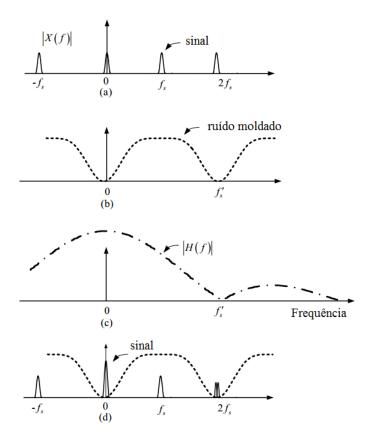

Nas Figuras 4.1 e 4.2 podemos observar as funções de transferência para um SDM tradicional e o PSDM.

Figura 4.1: (a) Sinal X(f) (sólido), o ruído moldado (pontilhada) e a resposta em frequência da amostragem H(f) (tracejada-ponto); (b) Amostragem do sinal  $\bar{Y}(f)$ .

A frequência nas Figuras 4.1 e 4.2 (a) é a mesma para o SDM e PSDM. No entanto eles têm diferentes frequências para (b), (c) e (d).

Pode-se observar na Figura 4.2 que enquanto  $f_s$  é suficientemente maior que a frequência de Nyquist do sinal de entrada, x(t), o sinal na banda-base é de alta qualidade. A fórmula para a taxa de sobre-amostragem é dada pela Equação 4.1. BW é a banda do sinal, e OSR representa a taxa de sobre-amostragem.

$$OSR = \frac{f_s}{BW} \tag{4.1}$$

Um sinal de entrada sobre-amostrado não é necessário para que o SDM produza

Figura 4.2: (a) Sinal X(f) (sólido), (b) o ruído moldado (pontilhada), (c) resposta em frequência da amostragem H(f) (tracejada-ponto); (d) sinal de saída quando a frequência de amostragem  $f_s$  é diferente da frequência do clock  $f_s'$  do SDM.

um sinal de alta qualidade na banda-base. No entanto, é importante para o SDM trabalhar em altas frequências, como com sobre-amostragem de 256 vezes a frequência de Nyquist, a fim de mover o ruído de quantização para as altas frequências, e assim diminuir seu nível na banda útil do sinal.

O PSDM proposto tira vantagem disso pelo fato de que os SDMs podem processar amostras de entradas constantes por N períodos de clock. Assim, o PSDM pode processar N amostras constantes em paralelo para combinar o processamento de N SDMs tradicionais.

A ordem do PSDM é a mesma ordem do SDM tradicional utilizado no PSDM. No entanto, N será referido como o fator de desenrolamento do PSDM. Nas próximas seções, um PSDM de segunda ordem com N=2 é descrito.

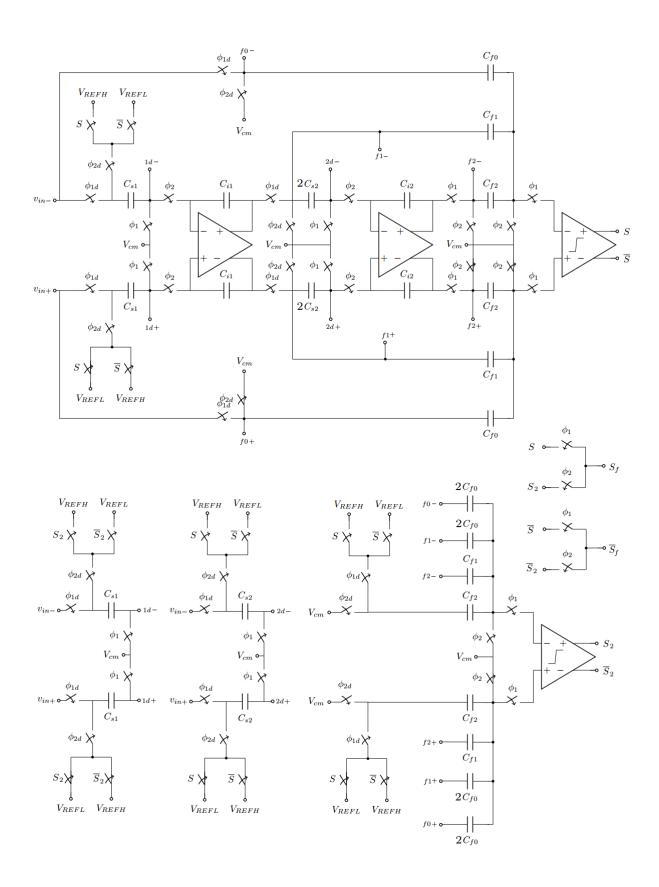

# 4.2 Implementação de um PSDM de Segunda Ordem e com Fator de Desenrolamento Dois

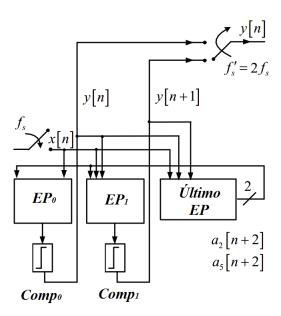

Nesta seção propõe-se a versão paralela de um SDM de segunda ordem, quando o fator desenvolamento, N, é igual a 2. A Figura 4.3 mostra o diagrama de blocos para essa implementação. A entrada do modulador sigma-delta é amostrada com a frequência  $f_s$ .

Figura 4.3: Diagrama de blocos da implementação de um PSDM de segunda ordem com fator de desenvolamento 2.

Note que o PSDM associado à Figura 4.3 processa uma entrada constante em N períodos de clock, no caso N é 2. Todos os elementos de processamento estão trabalhando a frequência de clock  $f_s$ . A frequência do multiplexador, que dá a taxa de transferência do PSDM, é  $f'_s$ =2 $f_s$ . Na verdade, a frequência efetiva do PSDM é  $f'_s$ =2 $f_s$  por causa do processamento paralelo. Esta característica do PSDM ajuda no seu projeto, pois os componentes que compõem o modulador terão que trabalhar com a metade da frequência de clock. Assim, seus requisitos de funcionamento serão reduzidos, pois estão trabalhando com uma frequência menor, e consequentemente dissipando menos energia.

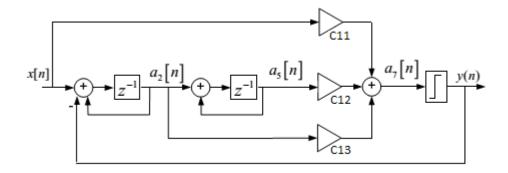

A Figura 4.4 apresenta a implementação do modulador sigma-delta de segunda ordem com os respectivos ganhos C11, C12 e C13.

Supõe-se que os sinais  $a_2[n]$ ,  $a_5[n]$ ,  $a_7[n]$ , x[n] e y[n] denotam os sinais nos nós na amostra de tempo n. Os sinais x[n] e y[n] referem-se aos sinais de entrada e de saída do SDM. Uma vez que é assumido que N=2, o sinal de entrada é constante durante dois ciclos de clock  $f'_s$ , ou seja, x[n] = x[n+1], onde n é um múltiplo de 2.

Figura 4.4: Representação de um SDM de segunda ordem.

As expressões na Equação 4.2 mostram como calcular os valores dos sinais  $a_2$ ,  $a_5$  e  $a_7$  no tempo n+1, utilizando os valores do sinal na amostra de tempo anterior, n. O valor do sinal  $a_7$  é calculado diretamente a partir de  $a_2$ ,  $a_5$  e x no tempo n. O quantizador de dois níveis quantiza  $a_7$  em -1 ou +1 no tempo n. O valor quantizado é y[n].

$$a_{2}[n+1] = a_{2}[n] + x[n] - y[n]$$

$$a_{5}[n+1] = a_{2}[n] + a_{5}[n]$$

$$a_{7}[n] = C13 \cdot a_{2}[n] + C12 \cdot a_{5}[n] + C11 \cdot x[n] \leftarrow EP_{0}$$

$$y[n] = Q(a_{7}[n]) \leftarrow Comp_{0}$$

$$(4.2)$$

As duas últimas linhas na Equação 4.2 correspondem às duas partes do PSDM na Figura 4.3, elemento processador  $(EP_0)$  e quantizador de 1 bit  $(Comp_0)$ .

As expressões na Equação 4.3 mostram como calcular os valores dos sinais  $a_2$ ,  $a_5$  e  $a_7$  no tempo n+2, utilizando os valores do sinal na amostra de tempo anterior, assumindo que o sinal de entrada, x, é contante no tempo n e n+1. Para atualizar os valores dos sinais para o próximo período de clock  $f'_s$ , as expressões utilizadas na Equação 4.2 têm seus valores no tempo incrementados como mostrado na Equação 4.3.

$$a_{7}[n+1] = (C12 + C13) \cdot a_{2}[n] + C12 \cdot a_{5}[n]$$

$$+ (C11 + C13) \cdot x[n] - C13 \cdot y[n] \leftarrow EP_{1}$$

$$y[n+1] = Q(a_{7}[n+1]) \leftarrow Comp_{1}$$

$$(4.3)$$

As linhas na Equação 4.3 correspondem às seguintes partes do PSDM na Figura 4.3, elemento processador  $(EP_1)$  e quantizador de 1 bit  $(Comp_1)$ , que calcula a saída y no tempo n+1.

Pode-se observar na equação que o procedimento de cálculo de  $a_7[n+1]$  pode

ser dividido em duas partes. A primeira parte é dependente dos valores dos sinais  $a_2$ ,  $a_5$  e x no tempo n e pode ser processada no tempo n. A segunda parte depende de y[n], que é processada por  $EP_1$ , e esse processo se inicia no tempo n. A segunda parte é um valor de dois níveis e as duas possibilidades podem ser pré-calculadas e armazenadas. Somente quando y[n] está pronto a segunda parte é multiplexada a partir dos valores pré-calculados. O único cálculo que depende de y[n] é o somatório do termo pré-calculado  $C13 \cdot y[n]$  e o cálculo da segunda parte da Equação 4.3.

Para concluir o processo de calcular duas saídas sequenciais do PSDM, deve-se iniciar o processo ao mesmo tempo para conseguir finalizá-lo em um período de clock  $f'_s$ . Está claro a partir das Equações 4.2 e 4.3 que os atrasos das duas saídas sequenciais são da mesma ordem que de um SDM tradicional, como observado nas primeiras duas linhas da Equação 4.2. A Figura 4.3 mostra como o processo do cálculo é feito pelo PSDM.

Os sinais  $a_2$  e  $a_5$  são computados pelas Equações 4.4 e 4.5, são usados nos próximos dois ciclos e correspondem ao último elemento processador mostrado na Figura 4.3.

$$a_{2}[n+2] = a_{2}[n+1] + x[n+1] - y[n+1]$$

$$a_{2}[n+2] = a_{2}[n] + x[n] - y[n] + x[n] - y[n+1]$$

$$a_{2}[n+2] = a_{2}[n] + 2 \cdot x[n] - y[n] - y[n+1]$$

$$(4.4)$$

$$a_{5}[n+2] = a_{2}[n+1] + a_{5}[n+1]$$

$$a_{5}[n+2] = a_{2}[n] + x[n] - y[n] + a_{2}[n] + a_{5}[n]$$

$$a_{5}[n+2] = 2 \cdot a_{2}[n] + a_{5}[n] + x[n] - y[n]$$

$$(4.5)$$

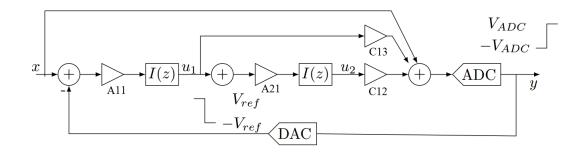

## 4.3 Modelagem do PSDM

Os principais componentes para o projeto do PSDM são os integradores, os coeficientes e o conversor digital para analógico (DAC). A definição dos seus parâmetros é fundamental para o seu funcionamento correto. Os parâmetros mais importantes do DAC são as tensões de referência utilizadas, pois estas determinam a faixa de tensão na saída do primeiro integrador e definem também o valor dos coeficientes de realimentação.

Os valores dos coeficientes restantes foram obtidos simulando o modelo ideal do modulador para cada combinação de coeficientes, buscando os valores máximos de SNR em uma dada amplitude de entrada. Os valores dos coeficientes ideais são os que proporcionam a máxima SNR e ocupam a menor área possível. As simulações foram feitas usando modelos de Simulink baseados em [26]. E como foi descrito na seção 4.2, o PSDM trata-se de uma versão paralela de um SDM de segunda ordem,

quando o fator de desenrolamento é igual a 2.

Na Figura 4.5 é mostrado o modelo do modulador de segunda ordem utilizado para o cálculo dos coeficientes.

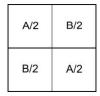

Figura 4.5: Representação de um SDM de segunda ordem.

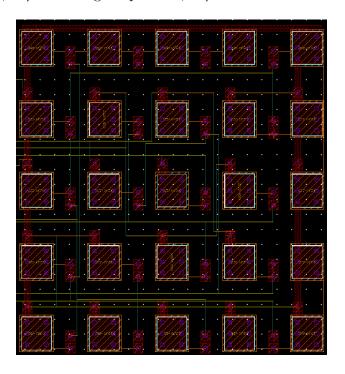

O objetivo foi encontrar o valor máximo de SNR para um sinal de entrada com amplitude igual a  $A_{in} = 0, 9 \cdot V_{REF}$ . O modelo ideal foi simulado para cada combinação dos coeficientes, A11 e A21 variaram de 0,1 a 0,9 com passos de 0,1 e, C12 e C13 variaram de 0,5 a 2,5 com passos de 0,25. Os coeficientes A11 e A21 são formados por uma razão entre as capacitâncias de chaveamento e de integração, enquanto que os coeficientes de feed-forward em moduladores de um bit são definidos pelo valor de um único capacitor. Na Tabela 4.1 são apresentados alguns dos valores obtidos com a varredura dos coeficientes. Neste trabalho foram utilizados os coeficientes: A11=0,9, A21=0,2, C12=1 e C13=1, pois o resultado da SNR necessária para essa aplicação é atingido com essa combinação e as razões de capacitâncias para esses valores dos coeficientes facilitarão o leiaute do PSDM.

Tabela 4.1: Coeficientes para obtenção do melhor SNR do modulador.

| SNR    | ENOB  | A11 | A21 | C12  | C13  |

|--------|-------|-----|-----|------|------|

| 105,04 | 17,16 | 0,8 | 0,2 | 0,75 | 1,25 |

| 105,03 | 17,16 | 0,8 | 0,8 | 1,25 | 1,25 |

| 105,00 | 17,15 | 0,8 | 0,6 | 0,75 | 1,25 |

| 104,99 | 17,15 | 0,9 | 0,2 | 1,00 | 1,00 |

| 104,95 | 17,14 | 0,6 | 0,3 | 1,75 | 1,00 |

| 104,89 | 17,13 | 0,8 | 0,2 | 1,25 | 1,75 |

| 104,62 | 17,09 | 0,9 | 0,3 | 2,00 | 2,00 |

As simulações a seguir foram feitas usando os parâmetros listados na Tabela 4.2. A tensão de referência  $V_{REF}$  é o nível de tensão de saída do DAC. Os parâmetros  $A_{in}$  e  $f'_{sin}$  são as características da entrada senoidal do modulador, sendo a freqüência

de entrada proporcional à resolução de frequência  $(f'_s/I)$  e próxima a 1,8 kHz que é a última componente de frequência do sinal medido.

Tabela 4.2: Parâmetros de simulação.

| Parâmetro                 | Símbolo   | Valor                       |

|---------------------------|-----------|-----------------------------|

| Constante de Boltzmann    | k         | $1,381 \times 10^{-23} J/K$ |

| Temperatura               | Τ         | 300 K                       |

| Número de Amostras        | I         | 65536                       |

| Tensão de referência      | $V_{REF}$ | 1 V                         |

| Frequência de Amostragem  | $f_s$     | $512~\mathrm{kHz}$          |

| Amplitude do Sinal        | $A_{in}$  | $0, 9 \cdot V_{REF}$        |

| Frequência do Sinal       | $f_{sin}$ | $116 \cdot (f_s'/I)$        |

| Largura de Banda          | BW        | $(f_s/2)/OSR$               |

| Razão de Sobre-amostragem | OSR       | 128                         |

|                           |           |                             |

#### 4.3.1 Resposta do PSDM Ideal

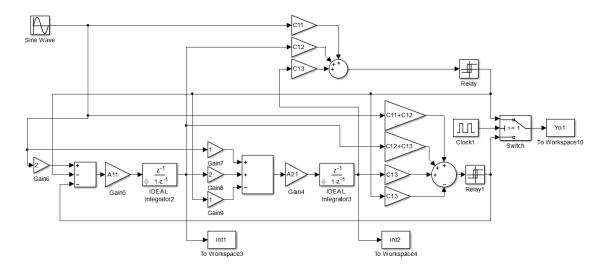

As simulações foram primeiramente realizadas usando o modelo do PSDM em simulink mostrado na Figura 4.6, utilizando os coeficientes definidos anteriormente da seguinte maneira A11=0,9, A21=0,2, C11=1, C12=1 e C13=1.

Figura 4.6: Modelo em Simulink ideal do PSDM de segunda ordem com fator de desenrolamento 2.

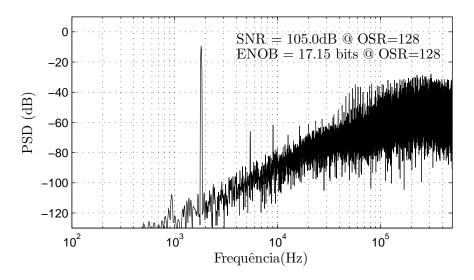

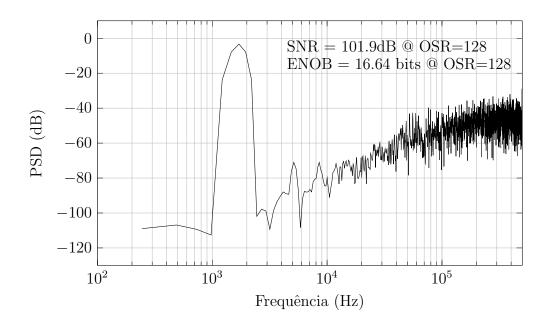

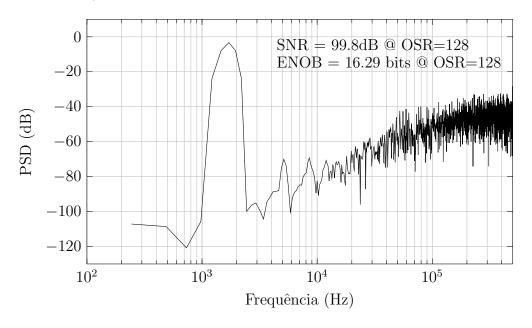

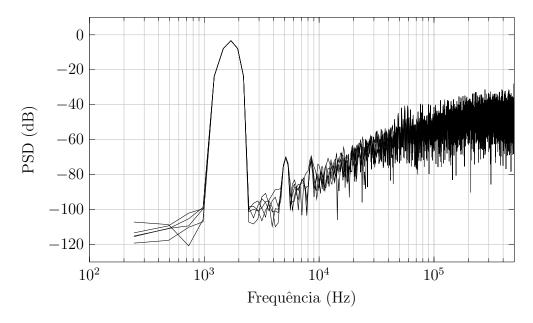

A densidade espectral de potência (PSD) do sinal de saída é mostrada na Figura 4.7. Como pode ser observado, para o modelo ideal foi atingida uma SNR de 104,99 dB com um número efetivo de bits (ENOB) de 17,15.

Figura 4.7: Resposta em frequência para o modelo em Simulink ideal do PSDM de segunda ordem com fator de desenrolamento 2, com os valores de SNR e ENOB.

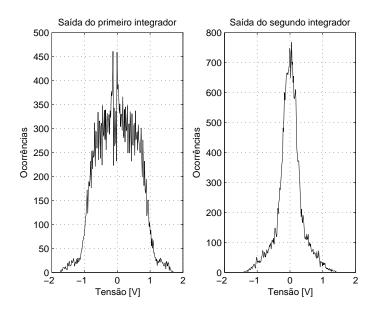

Os histogramas das saídas dos integradores são mostrados na Figura 4.8. Podese observar que a tensão de saída do primeiro integrador varia de -1,74 a 1,74 e do segundo integrador vai de -1,44 a 1,44. Ambos estão na faixa de resposta típica do amplificador, o que significa que não são necessárias técnicas especiais para o projeto deste circuito.

Figura 4.8: Histogramas das saídas dos integradores.

#### 4.3.2 Resposta do PSDM Não-Ideal

As não idealidades do amplificador, como o ganho DC  $(A_{DC})$ , a máxima taxa de variação da tensão de saída (SR), o produto ganho-banda (GBW) e a tensão de saturação  $(V_{SAT})$  são as causas da transferência incompleta de carga em um integrador a capacitores chaveados.

O ruído do integrador é a principal causa da degradação da SNR no modulador, por isso as não-idealidades devem ser especificadas considerando a preservação da resposta ideal do circuito. Esses efeitos foram analisados e modelados em [26], [27].

Em [28], foram definidas as não idealidades do amplificador que funcionava com uma frequência de 1 MHz. Nessa tese como o objetivo do modulador desenvolvido é reduzir o consumo de energia, um dos meios para se atingir esse objetivo é reduzir os requisitos do amplificador e isso é atingido pela diminuição da frequência de sobre-amostragem, pois trabalhando com uma menor frequência de chaveamento o amplificador poderá ser projetado com técnicas que obtêm um menor consumo de energia. Como nesse trabalho a frequência é de 512 kHz, alguns desses parâmetros podem ser utilizados de acordo com a Tabela 4.3.

Tabela 4.3: Especificações do amplificador.

| Parâmetro | [28]                 | Este trabalho    |

|-----------|----------------------|------------------|

| $A_{DC}$  | > 56.9  dB           | > 56.9  dB       |

| GBW       | $> 3.2 \mathrm{MHz}$ | > 1,6 MHz        |

| SR        | > 21  MV/s           | $> 10.5 \; MV/s$ |

| $V_{SAT}$ | > 1,6 V              | > 1,74 V         |

Como pode ser observado, as especificações do amplificador utilizado nesse trabalho têm seus requisitos de GBW e SR diminuídos devido a se trabalhar com uma frequência menor e isso acarreta na diminuição do consumo de energia pois esses parâmetros estão diretamente ligados à quantidade de corrente utilizada pelo amplificador.

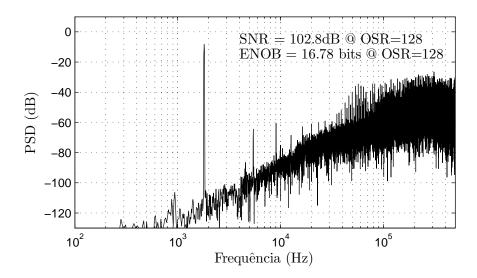

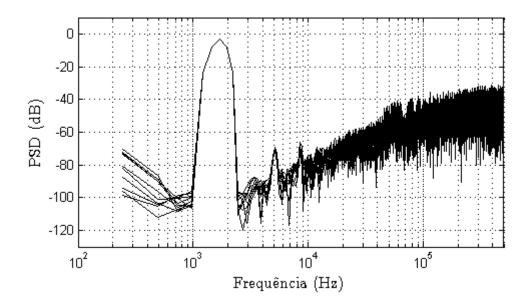

O modelo Simulink não-ideal demonstrado foi simulado usando os valores listados na Tabela 4.3. A PSD do sinal de saída é mostrada na Figura 4.9.

Figura 4.9: Resposta em frequência para o modelo em Simulink não-ideal do PSDM de segunda ordem com fator de desenrolamento 2, com os valores de SNR e ENOB.

Como pode se observar não há uma diferença significativa entre a reposta ideal mostrada na Figura 4.7 e a resposta obtida pelo modelo com parâmetros reais. A SNR do modulador difere do ideal em apenas 0,37 dB. O histograma de cada saída do integrador não é apresentado pois tem a mesma resposta que a do modelo ideal. Isto é esperado devido aos parâmetros não ideais do amplificador terem sido escolhidos de maneira que a resposta ideal do modulador não fosse afetada.

# Capítulo 5

## Projeto do PSDM

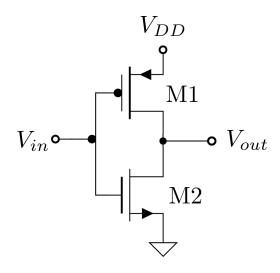

Neste capítulo descreve-se o projeto dos circuitos analógicos utilizados no PSDM para a tecnologia AMS 0,18  $\mu$ m e utilizando uma tensão de alimentação de 1,8 V. O projeto foi feito usando transistores padrão da tecnologia e priorizando a eficiência de energia ao invés da área. O procedimento para obter as dimensões finais dos transistores foi baseado em simulações.

## 5.1 Circuitos a Capacitores Chaveados

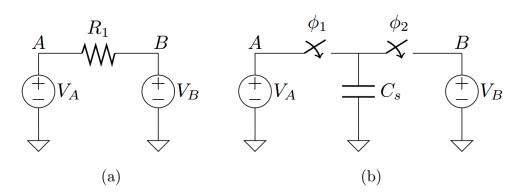

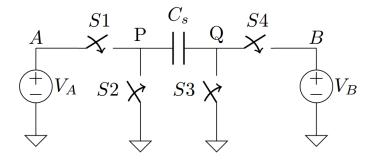

A idéia principal da técnica de capacitores chaveados consiste na substituição de resistores por capacitores acionados por chaves, permitindo a redução de área de silício e o aumento da precisão na implementação dos circuitos. O resistor mostrado na Figura 5.1 é simulado com o uso de um capacitor e um par de chaves analógicas que são acionadas de forma alternada e não simultânea.

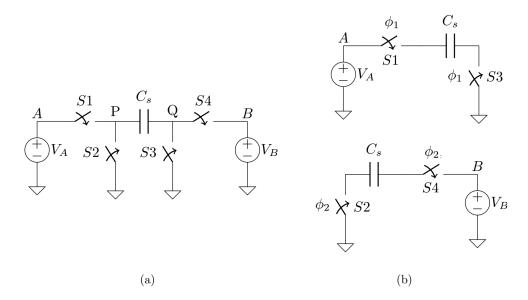

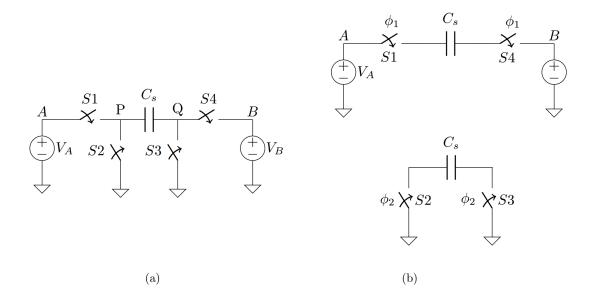

Figura 5.1: (a) Resistor ideal a ser simulado, (b) com a técnica de capacitores chaveados.

A aplicação do circuito chaveado melhora a precisão do sistema, pois a incerteza da razão entre dois capacitores é menor que a incerteza da razão entre um resistor e um capacitor, numa mesma pastilha de circuito integrado [29].

Para o circuito da Figura 5.1, na fase  $\phi_1$ , a chave 1 é fechada e a chave 2 é aberta e, na fase  $\phi_2$ , alternam os respectivos estados. As fases  $\phi_1$  e  $\phi_2$  que comandam o fechamento das chaves são pulsos com período igual a T. Na fase  $\phi_1$ , o capacitor  $C_s$  é carregado com a tensão  $V_A$ . Na transição de fases, ao abrir a chave 1, o capacitor continua armazenando a carga  $Q_1 = C_s \cdot V_A$ . Em seguida, ocorre o fechamento da chave 2, e a carga armazenada no capacitor se torna  $Q_2 = C_s \cdot V_B$ . Assim, a carga transferida de  $V_A$  até  $V_B$  em cada período de tempo T é dada pela Equação 5.1.

$$\Delta Q = C_s \cdot (V_A - V_B) \tag{5.1}$$

Se este processo de chaveamento é repetido n vezes no tempo, obtém-se:

$$\frac{\Delta q}{\Delta t} = C_s \cdot (V_A - V_B) \cdot \frac{n}{\Delta t} \tag{5.2}$$

Na última equação, considerando-se a corrente e a frequência de relógio, obtémse:

$$i = C_s \cdot (V_A - V_B) \cdot f_{clk} \tag{5.3}$$

Determina-se dessa forma o valor da resistência equivalente da estrutura com capacitor chaveado.

$$\frac{(V_A - V_B)}{i} = R = \frac{1}{C_s \cdot f_{clk}} \tag{5.4}$$

O valor da resistência equivalente é inversamente proporcional à frequência de chaveamento e à capacitância, o que possibilita aplicações flexíveis em filtros e conversores analógico-digitais. O resistor a capacitor chaveado mostrado na Figura 5.1, por ser muito sensível a capacitâncias parasitas, possui pouco uso em projeto de circuitos integrados. Outra estrutura a capacitor chaveado é mostrada na Figura 5.2. Esse arranjo é um dos mais adotados como solução para simulação de resistores, pois apresenta menor sensibilidade a capacitâncias parasitas que a estrutura da Figura 5.1.

Outra vantagem da configuração mostrada na Figura 5.2 é que esta é útil quando se precisa inverter a tensão de entrada  $(V_A)$ , que depende da operação das chaves. O módulo da resistência equivalente desta estrutura é dado pela Equação 5.4. Para inverter a tensão de entrada, uma carga de  $V_A$  é inicialmente acumulada no capacitor

Figura 5.2: Resistor simulado com a técnica de capacitores chaveados.

$C_S$ , operação realizada quando as chaves S1 e S3 são ativadas pela fase de relógio  $\phi_1$ . Em um segundo momento, as chaves S2 e S4 são ativadas por  $\phi_2$ , e uma tensão com polaridade invertida é injetada na saída do circuito. Esse processo pode ser observado na Figura 5.3.

Figura 5.3: (a) Resistor simulado (b) com inversão do sinal.