# UM ESTUDO SOBRE O MECANISMO CORTICAL DO DIFFUSIVE FILLING-IN EM SILÍCIO

Genildo Nonato Santos

Tese de Doutorado apresentada ao Programa de Pós-graduação em Engenharia Elétrica, COPPE, da Universidade Federal do Rio de Janeiro, como parte dos requisitos necessários à obtenção do título de Doutor em Engenharia Elétrica.

Orientador: José Gabriel Rodríguez Carneiro Gomes

Rio de Janeiro Setembro de 2016

# UM ESTUDO SOBRE O MECANISMO CORTICAL DO DIFFUSIVE FILLING-IN EM SILÍCIO

#### Genildo Nonato Santos

TESE SUBMETIDA AO CORPO DOCENTE DO INSTITUTO ALBERTO LUIZ COIMBRA DE PÓS-GRADUAÇÃO E PESQUISA DE ENGENHARIA (COPPE) DA UNIVERSIDADE FEDERAL DO RIO DE JANEIRO COMO PARTE DOS REQUISITOS NECESSÁRIOS PARA A OBTENÇÃO DO GRAU DE DOUTOR EM CIÊNCIAS EM ENGENHARIA ELÉTRICA.

| Examinada por: |                                                    |

|----------------|----------------------------------------------------|

|                |                                                    |

|                | Prof. José Gabriel Rodríguez Carneiro Gomes, Ph.D. |

|                | Prof. Antonio Petraglia, Ph.D.                     |

|                | Prof. Carlos Augusto Duque, D.Sc.                  |

|                | Prof. Fernando Antonio Pinto Barúqui, D.Sc.        |

|                | Prof. Mário Fiorani Junior, D.Sc.                  |

|                | Prof. Ricardo Guerra Marroquim, D.Sc.              |

RIO DE JANEIRO, RJ – BRASIL SETEMBRO DE 2016

#### Santos, Genildo Nonato

Um Estudo sobre o Mecanismo Cortical do Diffusive Filling-In em Silício/Genildo Nonato Santos. – Rio de Janeiro: UFRJ/COPPE, 2016.

XIX, 153 p.: il.; 29,7cm.

Orientador: José Gabriel Rodríguez Carneiro Gomes Tese (doutorado) – UFRJ/COPPE/Programa de Engenharia Elétrica, 2016.

Referências Bibliográficas: p. 79 – 84.

- Diffusive Filling-In.

Spiking Neural Network.

CMOS Neuron Models.

- 5. Amplitude Mode Simulation. 6. Spike Mode Simulation. I. Gomes, José Gabriel Rodríguez Carneiro.

- II. Universidade Federal do Rio de Janeiro, COPPE, Programa de Engenharia Elétrica. III. Título.

#### Dedico esta Tese:

Primeiramente a Deus, que permitiu todas as graças alcançadas;

Aos meus pais, que sempre me apoiaram e me deram forças;

A minha família, que sempre esteve ao meu lado.

## Agradecimentos

Agradeço ao meu orientador, o professor José Gabriel Rodríguez Carneiro Gomes pelo aprendizado e a sua constante disposição que possibilitou o desenvolvimento deste trabalho. Aos meus colegas F. Mederos, F. Duarte, A. Bides, J. Alberto e T. Brito do laboratório de processamento digital e analógico de sinais (PADS) pelas dicas de utilização das ferramentas e pelo apoio como amigos. Ao aprendizado transmitido pelos professores: A. Mesquita, A. Moreirão, A. Petraglia, M. Petraglia, A. Barúqui, R. Marroquim. Aos colegas e amigos do laboratório PADS da Universidade Federal de Rio de Janeiro pelo agradável ambiente de trabalho, que contribuíram direta ou indiretamente neste trabalho. A todos os que contribuiram diretamente e indiretamente para que eu pudesse concluir esse trabalho de Tese. À minha família, que sempre proporcionou carinho e apoio.

Resumo da Tese apresentada à COPPE/UFRJ como parte dos requisitos necessários para a obtenção do grau de Doutor em Ciências (D.Sc.)

## UM ESTUDO SOBRE O MECANISMO CORTICAL DO DIFFUSIVE FILLING-IN EM SILÍCIO

#### Genildo Nonato Santos

Setembro/2016

Orientador: José Gabriel Rodríguez Carneiro Gomes

Programa: Engenharia Elétrica

Para executar simulações de circuitos corticais em modo pulsado, isto é, considerando o sinal neural em termos de sequências de pulsos, o uso de hardware dedicado é recomendado. Muitos problemas estão envolvidos no projeto do hardware dedicado, o alto nível de complexidade de hardware para implementações de redes neurais pulsadas é um exemplo. As conexões entre os neurônios em uma rede neural pulsada se tornam impraticáveis sem a redução da quantidade de conexões. O axônio compartilhado ou SA é uma técnica de multiplexação no tempo que permite redução da quantidade de conexões. Contudo, o SA pode mudar significativamente a informação processada pela rede neural pulsada por causa de atrasos inseridos aleatoriamente no sinal. A simulação de circuitos corticais, com intuito de especificar o projeto do hardware dedicado, costuma ser conduzida em modo de amplitude, onde a informação neural é representada por uma sequência de valores escalares que descrevem as taxas de disparo dos neurônios. Ao representar sinais neurais por sequências discretas contendo taxas de disparo, a simulação em modo de amplitude não captura importantes características da dinâmica neural. Propomos uma abordagem que permite níveis mínimos de complexidade de hardware que causa baixa distorção, simulações em modo de amplitude e pulsado dos circuitos corticais que compõem o mecanismo cortical do diffusive filling-in. Essas simulações mostram que os resultados do modo de amplitude se aproximam bem dos resultados do modo pulsado. Utilizamos estímulos, estimados a partir de simulações de uma retina, não ideais que realçam as diferenças entre o modo de amplitude e o modo pulsado. Simulações mostram que a latência foi reduzida e sugerem que o modo de amplitude é confiável para realizar a análise de resultados de simulação em projetos de hardware customizado para simulações de circuitos corticais.

Abstract of Thesis presented to COPPE/UFRJ as a partial fulfillment of the requirements for the degree of Doctor of Science (D.Sc.)

# A STUDY ABOUT DIFFUSIVE FILLING-IN CORTICAL MECANISM IN SILICON

Genildo Nonato Santos

September/2016

Advisor: José Gabriel Rodríguez Carneiro Gomes

Department: Electrical Engineering

To run cortical circuit simulations in spike mode, i.e. taking into account the neural representation of information in terms of sequences of pulses (spikes), the use of customized hardware is recommended. Many problems are involved with this customized hardware design, for example, high hardware complexity is involved in the implementation of the spiking neural networks. Point-to-point connections between neurons in spiking neural networks becomes impractical without the use of hardware-level complexity reduction methods, e.g. shared axon or SA, which is a kind of time multiplexing technique. The SA technique randomly inserts delays in neural network spike sequences, which may lead to information loss. These delays are called latency. Simulation results are important for optimized hardware design. The simulations are carried out in amplitude mode. In amplitude mode information is represented by sequences of scalar values that describe neural input and output spike rates. However, by representing neural signals by conventional discrete sequences containing neural firing rates, the amplitude-mode simulation approach does not capture important features of neural dynamics. We propose a lower-latency approach which reduces to a minimum the hardware-level complexity. We carry out amplitude and spike-mode simulations of a cortical algorithm, namely the diffusive filling-in algorithm, to investigate whether the amplitude-mode results approximate well the spike-mode results. We used a non-ideal input, estimated from simulations of a retina, that highlights the differences between the amplitude and spike-mode approaches. Simulation results show that the latency was reduced and suggest that the amplitude mode is reliable for theoretical predictions, which are useful for customized hardware design for cortical circuit simulations.

## Sumário

| Li | sta d | le Figuras                                         | X     |

|----|-------|----------------------------------------------------|-------|

| Li | sta d | de Tabelas                                         | xvii  |

| Li | sta d | de Abreviaturas x                                  | cviii |

| 1  | Inti  | rodução                                            | 1     |

|    | 1.1   | Motivações                                         | 2     |

|    | 1.2   | Problemática                                       | 3     |

|    | 1.3   | Objetivos                                          | 4     |

|    | 1.4   | Metodologia de Trabalho                            | 5     |

| 2  | O E   | EVS e os Estímulos para o DFI                      | 7     |

|    | 2.1   | Modelo para a OPL                                  | 8     |

|    |       | 2.1.1 A OPL em uma Implementação CMOS              | 12    |

|    | 2.2   | Modelo para a IPL                                  | 17    |

|    | 2.3   | Modelo para a Camada de Células Ganglionares       | 19    |

|    | 2.4   | Resultados para a OPL e a IPL                      | 21    |

|    | 2.5   | Conclusões                                         | 24    |

| 3  | O N   | Nervo Óptico e a Técnica AER                       | 26    |

|    | 3.1   | Elementos de um Sistema AER                        | 27    |

|    | 3.2   | Latência em Sistemas AER                           | 38    |

|    | 3.3   | Complexidade de Hardware em Sistemas AER           | 40    |

|    | 3.4   | Comparação entre Sistemas AER                      | 42    |

|    | 3.5   | Técnica AER Proposta                               | 43    |

|    | 3.6   | Resultados para o AER NAP                          | 48    |

|    | 3.7   | Conclusões                                         | 49    |

| 4  | A F   | Retina CMOS                                        | 50    |

|    | 4.1   | Dimensões dos Transistores MOS para o AER Proposto | 54    |

|    | 4 2   | Resultados de Reconstrução do AER Proposto         | 57    |

| 4.3    | Resposta ao Impulso do AER Proposto                               | 58                                                                                                                                                                                                                                                                                                                |

|--------|-------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.4    | Estímulos para o Mecanismo Cortical                               | 58                                                                                                                                                                                                                                                                                                                |

| 4.5    | Conclusões                                                        | 60                                                                                                                                                                                                                                                                                                                |

| Circ   | cuitos Corticais Pulsados                                         | 63                                                                                                                                                                                                                                                                                                                |

| 5.1    | O Neurônio, a Representação no Tempo e o Processamento Pulsado  . | 64                                                                                                                                                                                                                                                                                                                |

| 5.2    | Modelo do Diffusive Filling-In                                    | 67                                                                                                                                                                                                                                                                                                                |

|        | 5.2.1 Detalhes sobre o DFI                                        | 69                                                                                                                                                                                                                                                                                                                |

| 5.3    | Resultados do DFI                                                 | 73                                                                                                                                                                                                                                                                                                                |

| 5.4    | Conclusões                                                        | 73                                                                                                                                                                                                                                                                                                                |

| Con    | aclusões e Trabalhos Futuros                                      | <b>7</b> 6                                                                                                                                                                                                                                                                                                        |

| 6.1    | Contribuições                                                     | 77                                                                                                                                                                                                                                                                                                                |

| 6.2    | Trabalhos Futuros                                                 | 78                                                                                                                                                                                                                                                                                                                |

| eferê: | ncias Bibliográficas                                              | <b>7</b> 9                                                                                                                                                                                                                                                                                                        |

| Scri   | pts Ocean                                                         | 85                                                                                                                                                                                                                                                                                                                |

| A.1    | Script Diagonal                                                   | 85                                                                                                                                                                                                                                                                                                                |

| A.2    | Script Impulso no Espaço e no Tempo                               | 132                                                                                                                                                                                                                                                                                                               |

| A.3    | Gerador de Scripts                                                | 149                                                                                                                                                                                                                                                                                                               |

|        |                                                                   |                                                                                                                                                                                                                                                                                                                   |

|        | 4.4 4.5 Circ 5.1 5.2 5.3 5.4 Con 6.1 6.2 eferê: Scri A.1 A.2 A.3  | 4.4 Estímulos para o Mecanismo Cortical 4.5 Conclusões  Circuitos Corticais Pulsados  5.1 O Neurônio, a Representação no Tempo e o Processamento Pulsado  5.2 Modelo do Diffusive Filling-In 5.2.1 Detalhes sobre o DFI  5.3 Resultados do DFI  5.4 Conclusões  Conclusões e Trabalhos Futuros  6.1 Contribuições |

# Lista de Figuras

| 2.1 | Diagrama em blocos do EVS. É apresentada a OPL, a IPL, a camada                 |    |

|-----|---------------------------------------------------------------------------------|----|

|     | de células ganglionares e os respectivos sinais em suas entradas e              |    |

|     | saídas.                                                                         | 7  |

| 2.2 | Em um cabo dividido em elementos infinitesimais $(x)$ , de compri-              |    |

|     | mento $\Delta L$ , existe uma corrente que flui horizontalmente pelo cabo       |    |

|     | $(I_i(x))$ e uma corrente que é conduzida verticalmente pelo elemento           |    |

|     | infinitesimal $(I_m(x))$                                                        | 8  |

| 2.3 | Os componentes do modelo elétrico de um cabo são apresentados. Os               |    |

|     | elementos infinitesimais do cabo (capacitâncias e condutâncias) são             |    |

|     | conectados a partir de resistores $(R_i)$                                       | G  |

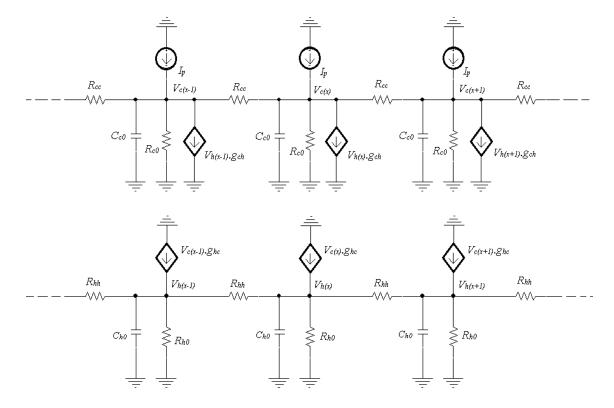

| 2.4 | Na parte superior da figura são mostrados o modelo elétrico de três             |    |

|     | fotorreceptores que compõem o modelo da rede de fotorreceptores,                |    |

|     | na figura da parte de baixo o modelo elétrico de três neurônios da              |    |

|     | rede de células horizontais. Fontes de corrente controlada por tensão           |    |

|     | (tensões $V_c(x)$ e $V_h(x)$ ) implementam as interações que ocorrem entre      |    |

|     | as duas redes                                                                   | 11 |

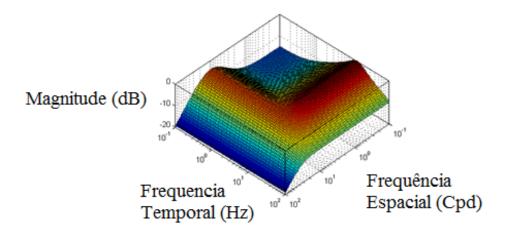

| 2.5 | Os parâmetros que definem a resposta da Eq. $(2.5)$ foram ajustados             |    |

|     | para que os picos em frequência espacial e temporal fossem de $10~\mathrm{Cpd}$ |    |

|     | e 10 Hz. O objetivo era o ajuste para 1 Cpd e 10 Hz, contudo, devido            |    |

|     | a limitações na quantidade de pontos no espaço da nossa simulação               |    |

|     | o valor de 1 Cpd teve que ser escalado para 10 Cpd                              | 12 |

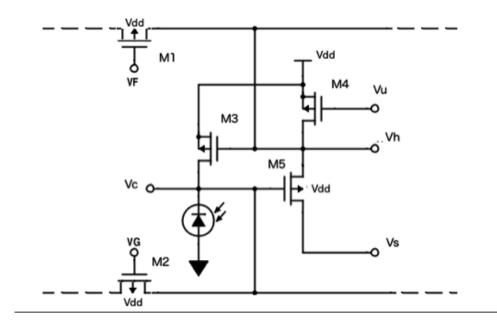

| 2.6 | Uma unidade da OPL CMOS equivalente a do diagrama esquemático                   |    |

|     | da Fig. 2.4. As fontes de corrente controladas por tensão e os resisto-         |    |

|     | res são substituídos por transistores MOS. Esse esquema foi adaptado            |    |

|     | de Boahen [16]                                                                  | 16 |

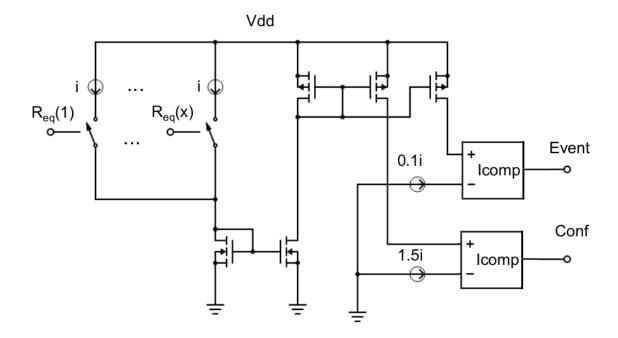

| 2.7 | Diagrama em blocos do EVS, em destaque a IPL, e diagrama esque-                 |    |

|     | mático do circuito retificador da IPL                                           | 18 |

|     |                                                                                 |    |

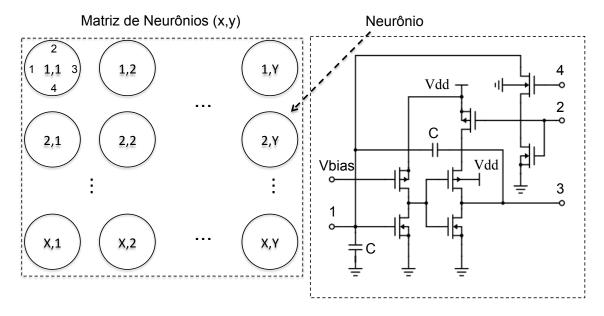

| 2.8          | Na estrutura apresentada temos a matriz de neurônios com $X \cdot Y$ neurônios, cada um deles numa posição $(x,y)$ . Ao lado da matriz é apresentada a estrutura interna de um desses peurônios. A figure foi |                                |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

|              | apresentada a estrutura interna de um desses neurônios. A figura foi adaptada de Boahen [32]                                                                                                                  | 20                             |

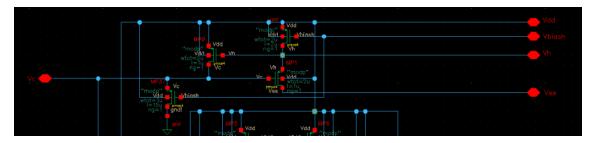

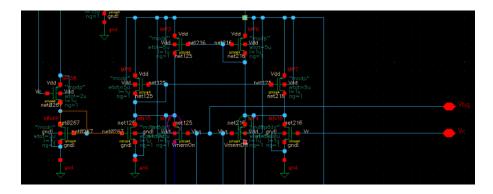

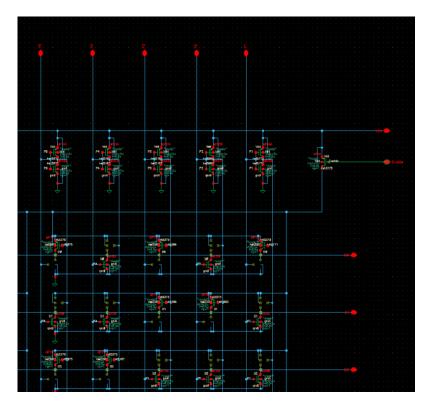

| 2.9          | Diagrama esquemático de uma unidade da OPL. Esse diagrama es-                                                                                                                                                 | 20                             |

| 2.5          | quemático ilustra a implementação do modelo elétrico, apresentado                                                                                                                                             |                                |

|              | na Fig. 2.6, feita na interface de desenvolvimento Cadence Virtuoso.                                                                                                                                          | 21                             |

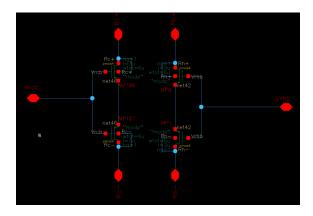

| 2.10         | A implementação na interface de desenvolvimento do diagrama es-                                                                                                                                               | <i>2</i> J                     |

| 2.10         | quemático dos pseudo-resistores $R_{hh}$ e $R_{cc}$                                                                                                                                                           | 22                             |

| 2.11         | Script que foi utilizado para realizar a simulação a partir da interface                                                                                                                                      | <i>Z</i> <sub>1</sub> <i>Z</i> |

| 2.11         | Ocean Script. O comando utilizado para alterar o valor das fontes de                                                                                                                                          |                                |

|              | corrente ik é o des Var                                                                                                                                                                                       | 22                             |

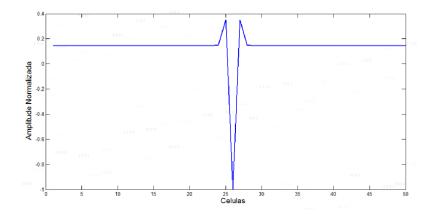

| າ 1າ         | Simulação elétrica da resposta da OPL 50x1 ao impulso no espaço.                                                                                                                                              | <i>Z</i> <sub>1</sub> <i>Z</i> |

| 2.12         | O eixo horizontal representa cada unidade da OPL. O esperado seria                                                                                                                                            |                                |

|              | 1                                                                                                                                                                                                             |                                |

|              | uma resposta semelhante à resposta ao impulso espacial de um filtro DoG, resposta conhecida como chapéu mexicano. Assim o formato                                                                             |                                |

|              | · · · · · ·                                                                                                                                                                                                   |                                |

|              | obtido é semelhante ao esperado. O formato está invertido devido                                                                                                                                              |                                |

|              | às características de polarização elétrica dos transistores MOS que                                                                                                                                           | 95                             |

| ი 1 <u>ე</u> | foram utilizados na implementação                                                                                                                                                                             | 23                             |

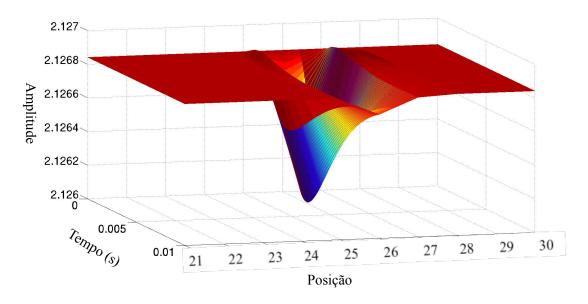

| 2.13         | A resposta do modelo elétrico da OPL (50x1) ao impulso no espaço                                                                                                                                              | 95                             |

| 0.14         | e no tempo. O impulso é aplicado à posição 26 do arranjo                                                                                                                                                      | 23                             |

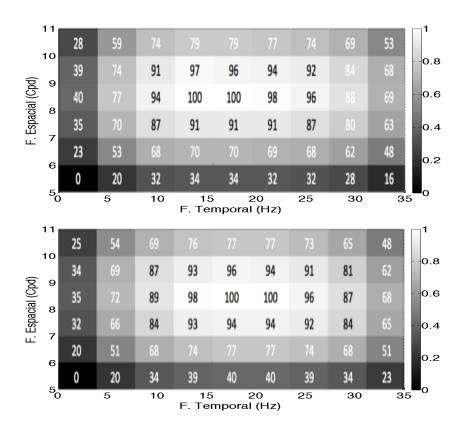

| 2.14         | A resposta espaço-temporal do modelo de uma OPL para estímulos                                                                                                                                                |                                |

|              | senoidais de valores variando no espaço e no tempo. A OPL foi proje-                                                                                                                                          |                                |

|              | tada para uma resposta passa banda espaço-temporal de 10 Cpd e 10                                                                                                                                             |                                |

|              | Hz. Na figura é mostrada a previsão teórica (em cima) e o resultado                                                                                                                                           |                                |

|              | da simulação elétrica (embaixo) que foi obtido ao simular o diagrama                                                                                                                                          |                                |

|              | esquemático da OPL que foi projetado a partir da metodologia pro-                                                                                                                                             | 0.4                            |

| 0.15         | posta.                                                                                                                                                                                                        | 24                             |

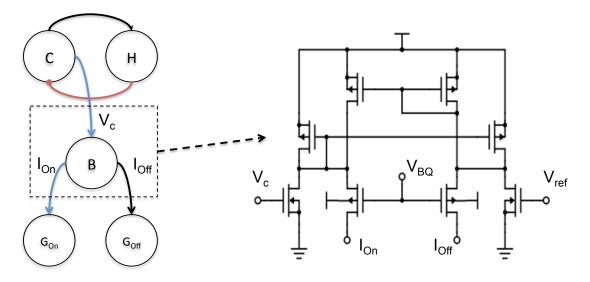

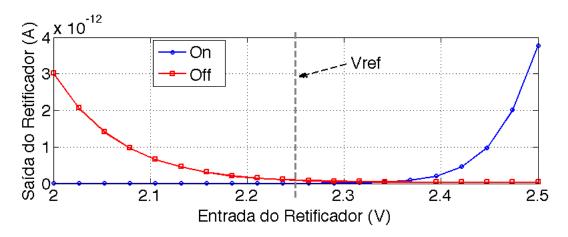

| 2.15         | Diagrama esquemático do modelo do retificador. O diagrama foi uti-                                                                                                                                            | 0.5                            |

| 0.46         | lizado para a realização de simulações elétricas.                                                                                                                                                             | 25                             |

| 2.16         | 1 00/                                                                                                                                                                                                         |                                |

|              | por um estímulo que varia de acordo com o sinal de saída do diagrama                                                                                                                                          |                                |

|              | esquemático da OPL, sinal $Vc$ . É possível verificar que, apesar de                                                                                                                                          |                                |

|              | certo nível de <i>off-set</i> de corrente, as respostas dos canais são separadas                                                                                                                              |                                |

|              | em relação a tensão de referência Vref                                                                                                                                                                        | 25                             |

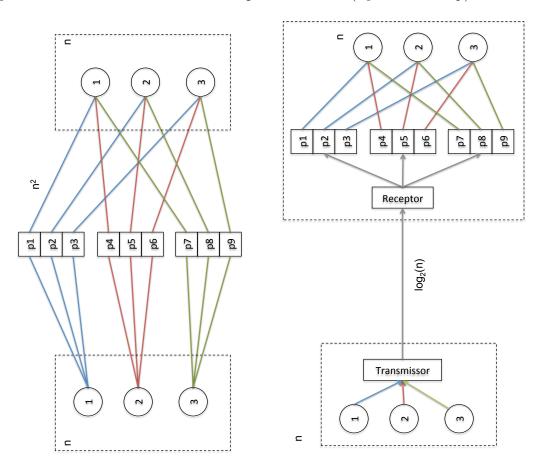

| 3.1 | Diferenças entre as topologias FD e SA. Considerando que os retângulos pontilhados são circuitos CMOS, onde cada um dos circuitos implementa três neurônios, à esquerda temos a topologia FD que |    |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | necessita de $n^2$ conexões, enquanto na topologia SA essa quantidade pode ser reduzida para um canal de comunicação de largura de $\log_2(n)$                                                   |    |

|     | bits                                                                                                                                                                                             | 26 |

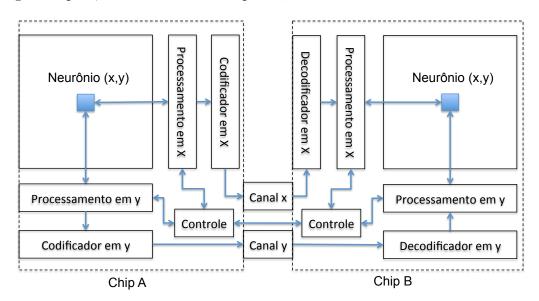

| 3.2 | A arquitetura de comunicação AER é apresentada. Elementos de processamento, elementos codificadores e um elemento de controle possibilitam que um evento gerado na matriz do estágio transmissor |    |

|     | seja enviado até a matriz do estágio receptor                                                                                                                                                    | 28 |

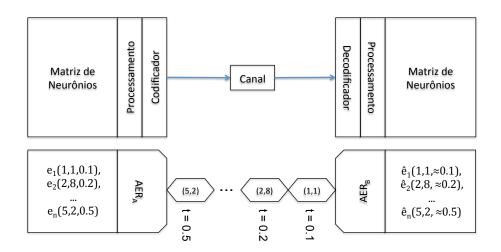

| 3.3 | Uma ilustração da arquitetura de comunicação AER onde $N$ eventos                                                                                                                                | 20 |

| 0.0 | $e_n, n = 1, 2, \dots, N$ , são transmitidos pelo canal de comunicação. Em                                                                                                                       |    |

|     | uma arquitetura AER, não é possível garantir que o evento $e_n$ seja                                                                                                                             |    |

|     | reconstruído perfeitamente em relação ao instante de tempo $t$ . A                                                                                                                               |    |

|     | figura foi adaptada de [12]                                                                                                                                                                      | 29 |

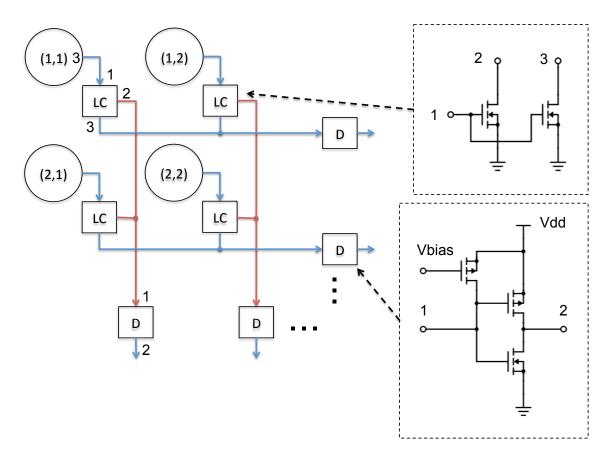

| 3.4 | Arquitetura dos elementos de processamento LC e D. Essa arquite-                                                                                                                                 |    |

|     | tura possibilita a redução da quantidade de conexões entre a matriz                                                                                                                              |    |

|     | de neurônios e o codificador. Um diagrama esquemático de cada ele-                                                                                                                               |    |

|     | mento é mostrado.                                                                                                                                                                                | 30 |

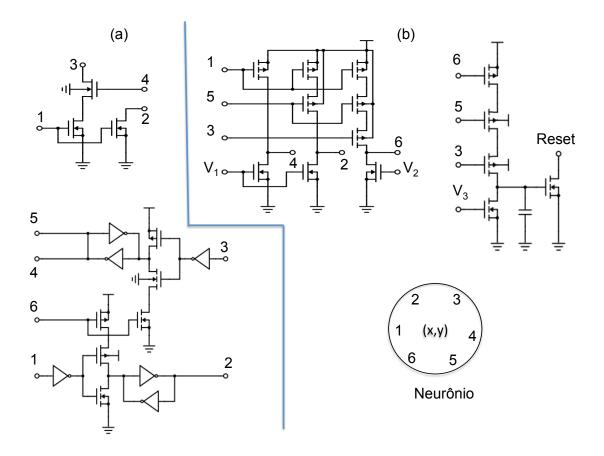

| 3.5 | A parte (a) da figura representa o diagrama esquemático das estruturas LC, no topo, e D, na parte inferior, utilizadas em Boahen [33].                                                           |    |

|     | Na parte (b) da figura [34] é apresentado um diagrama esquemático onde as estruturas LC, D e o neurônio formam um único bloco                                                                    | 31 |

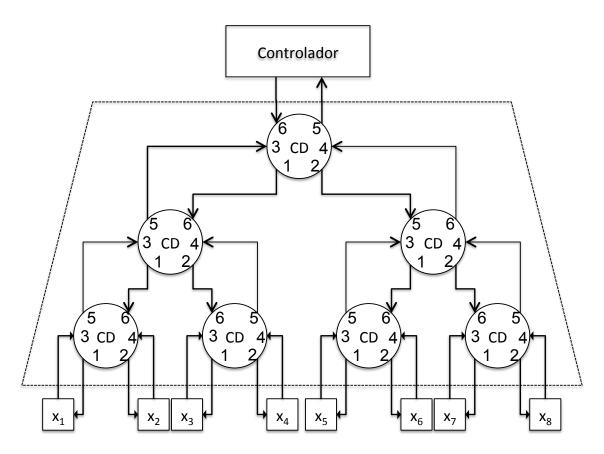

| 3.6 | A arquitetura de um árbitro AB que gerencia oito requisições (de $x_1$ até $x_8$ ). Os sinais de entrada $R_{eq}(A)$ , $R_{eq}(B)$ e $A_{ck}(In)$ são respectiva-                                |    |

|     | mente representados pelos terminais 3, 4 e 6. Os sinais de saída $Ack_A$ , $Ack_B$ e $R_{eq}(Out)$ são representados respectivamente pelos terminais                                             |    |

|     | $1, 2 e 5. \dots \dots \dots \dots \dots \dots \dots \dots \dots$                                                                                                                                | 33 |

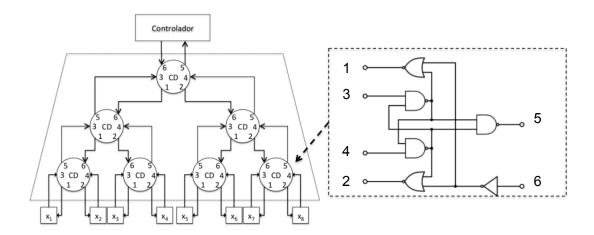

| 3.7 | A CD é composta por estruturas digitais biestáveis como a que é                                                                                                                                  |    |

|     | apresentada na figura à direita. À esquerda é apresentado um exemplo                                                                                                                             |    |

|     | de árvore binária. Os terminais dos elementos que compõem essa                                                                                                                                   |    |

|     | árvore binária estão de acordo com o que foi apresentado na Fig. 3.6.                                                                                                                            | 34 |

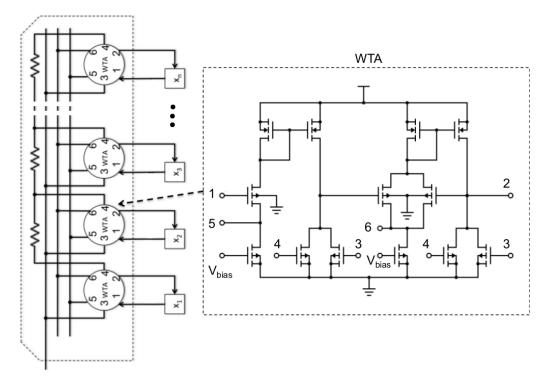

| 3.8 | Arquitetura utilizada no árbitro do tipo WTA proposto [34] (à es-                                                                                                                                |    |

|     | querda) e o diagrama esquemático de uma CD desse árbitro (À di-                                                                                                                                  |    |

|     | reita). Os sinais $ReqA$ ou $ReqB$ da CD da árvore binária são equi-                                                                                                                             |    |

|     | valentes ao sinal representado pelo terminal (1) e os sinais $AckA$ ou                                                                                                                           |    |

|     | AckB são equivalentes ao terminal (2). Os outros sinais são de con-                                                                                                                              |    |

|     | trole e polarização da estrutura                                                                                                                                                                 | 34 |

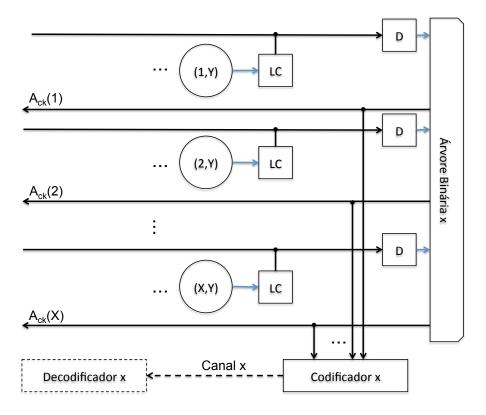

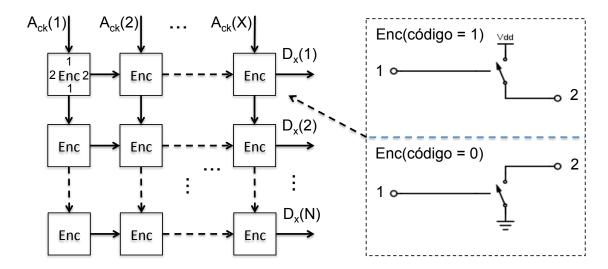

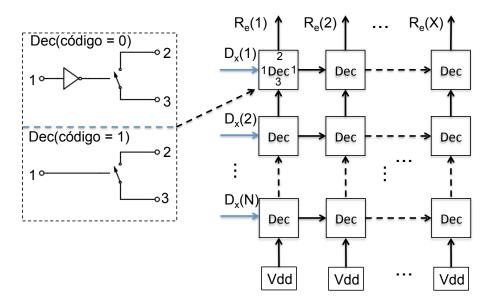

| 3.9  | O codificador recebe do árbitro os $X$ sinais $A_{ck}(x)$ e os codifica em um endereço composto de $\lceil \log_2(X) \rceil$ bits. Isso ocorre porque o árbitro faz com que, dos eventos entregues ao codificador, apenas um esteja ativo por vez                                  | 35         |

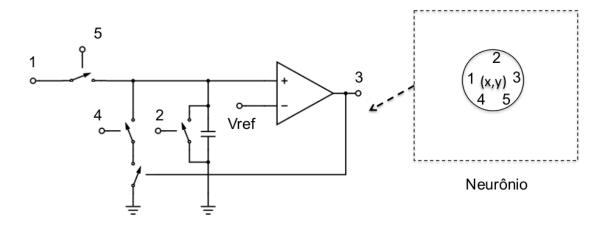

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 3.10 | No codificador o vetor de saída $D_X$ é uma função do vetor de entrada $A_{ck}$ , sendo que a função é definida dessas operações de codificação Enc. Dependendo do código a ser gerado as operações Enc podem ocorrer de duas formas diferentes, operações de código 1 e operações | 30         |

| 2 11 | de código 0                                                                                                                                                                                                                                                                        | 36         |

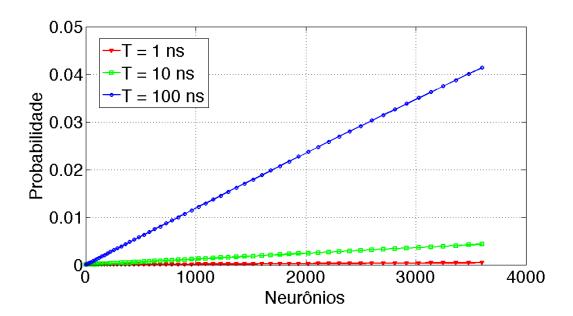

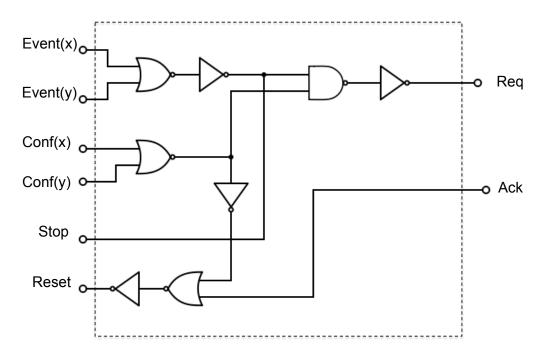

| 0.11 | é projetado de maneira que cada código recebido ative somente uma de suas saídas $R_e(x)$ , deixando as outras em estado de alta impedância.                                                                                                                                       | 37         |

| 3.12 | A probabilidade de colisão, com função de uma população de neurônios e com uma taxa de disparos de 100 Spk/s. São mostradas três                                                                                                                                                   |            |

| 3.13 | curvas, sendo cada uma delas para um dado $T$                                                                                                                                                                                                                                      | 44         |

| 3.14 | transistores, 1 transistor a mais do que na Fig. 2.8 Diagrama esquemático do gerenciador de eventos. Esse dispositivo é capaz de identificar quando um evento é gerado e se a quantidade de                                                                                        | 45         |

| 3.15 | eventos gerados é igual ou maior que dois                                                                                                                                                                                                                                          | 46         |

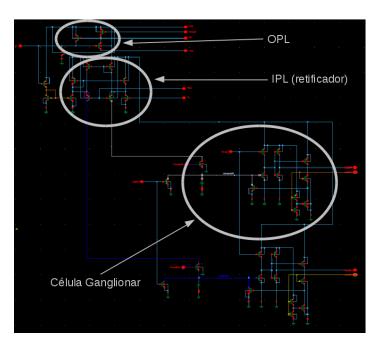

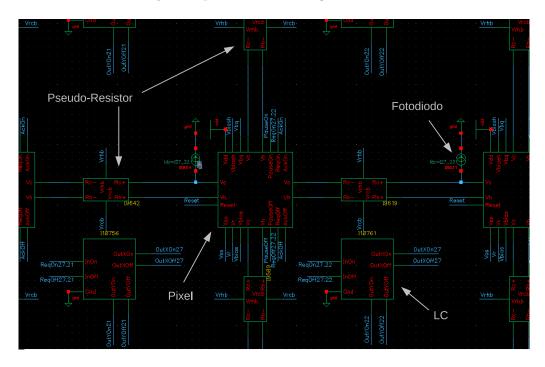

| 4.1  | A figura mostra o diagrama esquemático de um dos 50 x 50 pixels do imageador que foi utilizado para realização dos testes de simulação. Na figura é possível identificar os diagramas esquemáticos da OPL,                                                                         | <b>F</b> 0 |

| 4.2  | IPL e das células ganglionares                                                                                                                                                                                                                                                     | 50         |

| 4.3  | turas LC                                                                                                                                                                                                                                                                           | 51         |

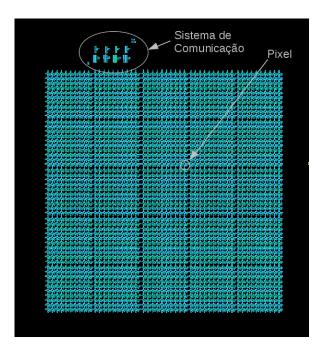

|      | Um pixel e o sistema de comunicação estão destacados                                                                                                                                                                                                                               | 51         |

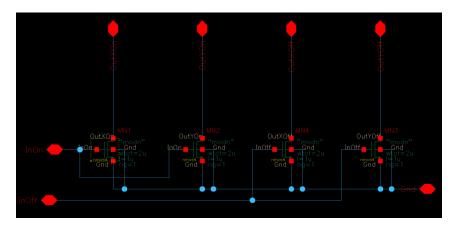

| 4.4  | Detalhes dos sinais e o diagrama esquemático da estrutura LC. Os                           |    |

|------|--------------------------------------------------------------------------------------------|----|

|      | sinais de entrada são InOn e InOff e os sinais de saída são OutXOn,                        |    |

|      | OutXOff, OutYOn e OutYOff                                                                  | 52 |

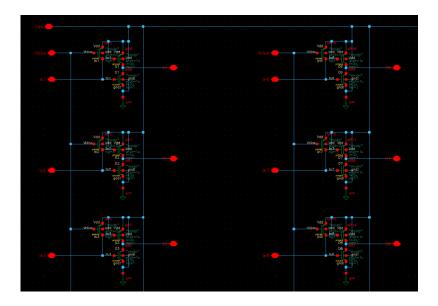

| 4.5  | A figura mostra o diagrama esquemático utilizado para a estrutura                          |    |

|      | D. Os sinais de saída da estrutura LC são recebidos a partir dos sinais                    |    |

|      | de entrada $\text{In} x$ e $\text{In} y$ . Os sinais de saída da estrutura D são os sinais |    |

|      | Ox e Oy. Com $x e y$ variando de 1 até 50                                                  | 52 |

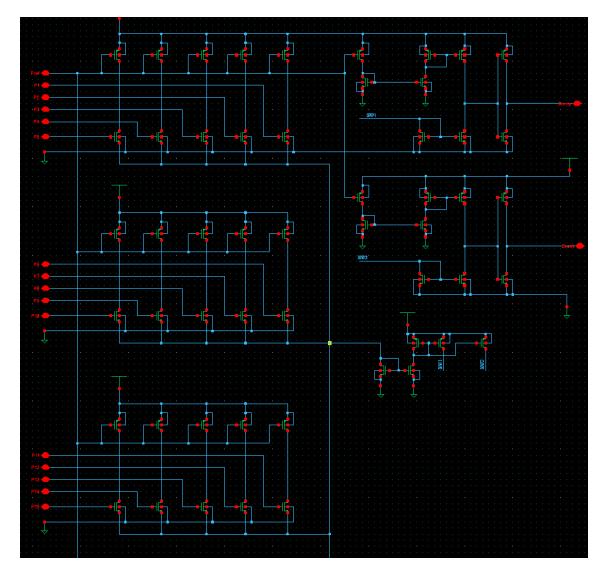

| 4.6  | Diagrama esquemático do sistema gerenciador de eventos proposto.                           |    |

|      | Na figura é possível identificar as entradas de P1 até P15 e as saídas                     |    |

|      | Event e Comp do sistema gerenciador de eventos                                             | 53 |

| 4.7  | A figura mostra a matriz do decodificador. Em destaque estão as                            |    |

|      | entradas de P1 até P5 e as saídas de D0 até D2                                             | 54 |

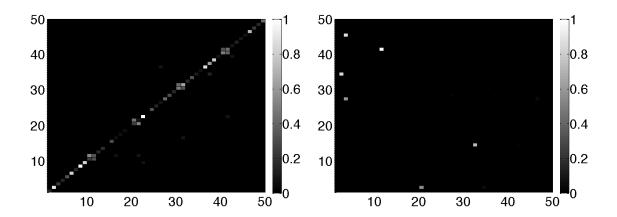

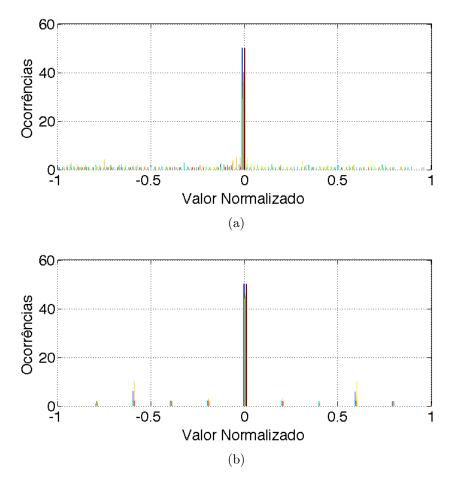

| 4.8  | Análise de Monte Carlo para verificação da perda de informação (a) e                       |    |

|      | descaracterização da taxa de disparo dos neurônios (b). Essa análise                       |    |

|      | foi feita sobre o sistema AER proposto                                                     | 55 |

| 4.9  | A reconstrução de um estímulo em diagonal aplicado ao sistema AER                          |    |

|      | proposto. Como a OPL foi desabilitada toda a informação deveria                            |    |

|      | passar pelo canal $On$ (esquerda). No entanto, é possível perceber                         |    |

|      | transmissões feitas pelo canal $O\!f\!f$ (direita). Apesar de algum ruído, a               |    |

|      | diagonal foi reconstruída a partir da informação de eventos aquisitada                     |    |

|      | no canal $On$                                                                              | 57 |

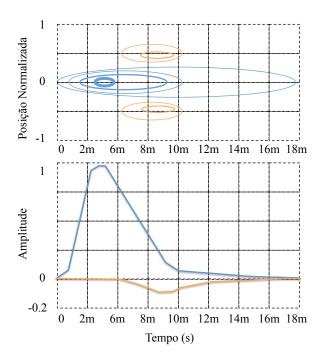

| 4.10 | O imageador é estimulado por um impulso no espaço e no tempo. A                            |    |

|      | resposta ao impulso do sistema AER proposto é mostrada em duas                             |    |

|      | vistas. É possível perceber as semelhanças entre os perfis da resposta                     |    |

|      | apresentada aqui e a resposta ao impulso de uma retina biológica                           |    |

|      | apresentada por Eggermont [36], Fig. 4.11                                                  | 58 |

| 4.11 | A resposta ao impulso de uma retina biológica que foi adaptada de                          |    |

|      | Eggermont [36]. Essa figura é utilizada como uma previsão teórica                          |    |

|      | do resultado esperado da resposta ao impulso do nosso imageador. É                         |    |

|      | possível perceber semelhanças entre a posições dos vales dos gráficos                      |    |

|      | apresentados aqui e os gráficos apresentados na Fig. 4.10                                  | 59 |

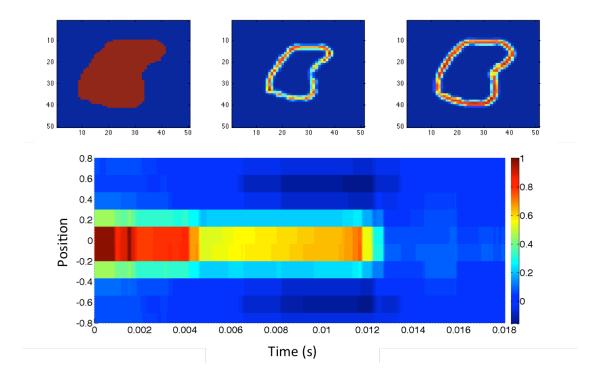

| 4.12 | A previsão teórica da resposta (superior, esquerda e meio), da si-                         |    |

|      | mulação elétrica, do processamento do imageador proposto sobre um                          |    |

|      | dado estímulo, coluna esquerda na linha superior. Na linha de baixo                        |    |

|      | é mostrada a resposta ao impulso do imageador                                              | 60 |

| 4.13 | A diversidade no valor das amostras causada nos sinais de estímulos do DFI após o processamento realizado pelo imageador proposto, um modelo elétrico da retina (a). Se esse processamento for substituído por aquele realizado por um filtro DOG (b), a diversidade não será tão grande e assim, nesse caso, os estímulos produzidos serão menos realistas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 61  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

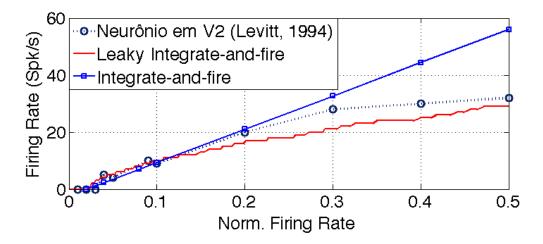

| 5.1  | Taxa de disparo na saída de um neurônio biológico (linha pontilhada) como função de uma taxa de entrada que corresponde a um contraste normalizado [41], e a aproximação da resposta de dois modelos para essa curva, LIF (linha sólida) e IF (linha com marcadores quadrados).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 65  |

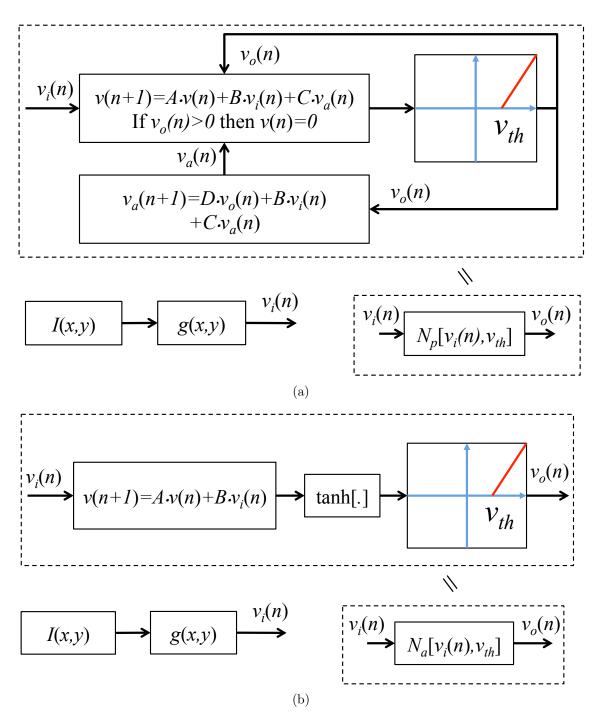

| 5.2  | Implementações do modo pulsado (a) e do modo de amplitude (b) de um exemplo computacional de um detector de bordas. A imagem de entrada $v_i(n)$ é obtida a partir da convolução, no domínio espacial, entre uma imagem de entrada $I(x,y)$ e um filtro passa alta $g(x,y)$ (nesse trabalho os filtros serão chamados de pesos sinápticos). No modo pulsado (a), A imagem de entrada $v_i(n)$ é utilizada como entrada de uma equação diferencial de acordo com o modelo do LIF in Eq. (5.1). No modo de amplitude (b), a equação diferencial usada corresponde ao modelo descrito pela Eq. (5.2)                                                                                                                                                                                                                                                                              | 66  |

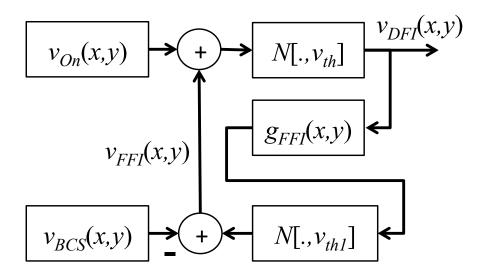

| 5.3  | O diagrama de blocos do algoritmo do DFI (em modo pulsado ou em modo de amplitude). Para gerar a imagem $v_{DFI}(x,y)$ a partir das imagens $v_{On}(x,y)$ , $v_{FFI}(x,y)$ e do nível de limiar $v_{th}$ , é utilizada a função de ativação $N[.]$ que foi indicada nas Figs. 5.2(a) e 5.2(b). A convolução com o peso $g_{FFI}(x,y)$ permite o espalhamento da atividade neural a partir de um pixel para os seus vizinhos. Um laço de realimentação é implementado por meio de um neurônio (o modelo). Esse laço permite que o espalhamento continue até tomar a imagem inteira. Contudo uma operação de subtração com a imagem de saída do estágio de processamento boundary contour system (BCS, mais detalhes a seguir) $v_{BCS}(x,y)$ faz com que o espalhamento pare. Em modo de amplitude temos que $v_{th} = v_{th1} = 0.01$ . Em modo pulsado $v_{th} = v_{th1} = 1$ | 67  |

|      | $\circ_{tn}$ $\circ_{tn_1}$ - $\dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | O I |

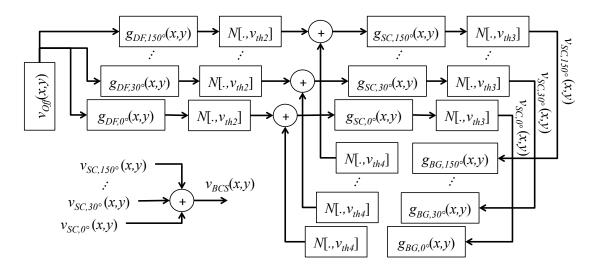

| 5.4 | Diagrama de blocos do BCS. A imagem de entrada é $v_{Off}(x,y)$ e a                |    |

|-----|------------------------------------------------------------------------------------|----|

|     | imagem de saída é $v_{BCS}(x,y)$ . Todas as operações são realizadas si-           |    |

|     | multaneamente ao longo dos canais orientados em $0^o$ , $30^o$ , $60^o$ , $90^o$ , |    |

|     | $120^o,$ e $150^o.$ A convolução com o filtro DF (direcional) seguido por          |    |

|     | uma operação de limiar com o nível $v_{th2}$ tende a manter os segmentos           |    |

|     | do contorno, em cada canal orientado, ao longo de uma direção em                   |    |

|     | particular. A convolução com o filtro SC (competição espacial) se-                 |    |

|     | guido da operação de limiar com o nível $v_{th3}$ remove segmentos fracos          |    |

|     | (residuais) que permaneceram do estágio de filtragem anterior, refor-              |    |

|     | çando os segmentos ao longo da correta orientação. A convolução com                |    |

|     | o filtro BG (agrupamento por bipolo) permite conectar segmentos de                 |    |

|     | contorno que devem ser unidos no mesmo contorno. Esses segmen-                     |    |

|     | tos possivelmente foram separados por causa das leituras defeituosas               |    |

|     | feitas pelo sistema visual precoce. Os resultados da operação BG re-               |    |

|     | forçam os resultados da operação SC e vice-versa. A saída do BCS é                 |    |

|     | obtida ao serem somadas as saídas de todos os canais SC                            | 70 |

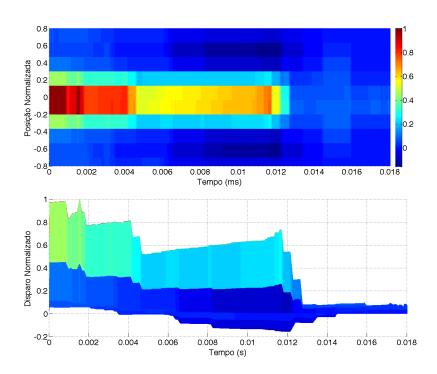

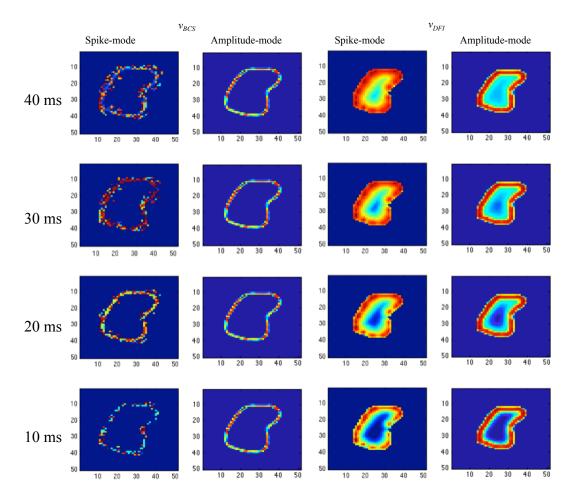

| 5.5 | Resultado das operações de BCS (as duas colunas a direita) e DFI                   |    |

|     | (as duas colunas a esquerda) em 4 diferentes instantes de tempo (10,               |    |

|     | 20, 30 e 40 mili-segundos). A primeira e a terceira colunas se referem             |    |

|     | aos resultados da implementação pulsada e as outras, aos resultados                |    |

|     | da implementação em modo de amplitude                                              | 74 |

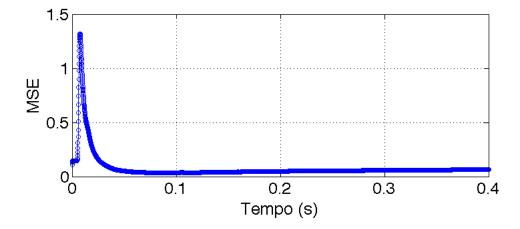

| 5.6 | Erro médio quadrático entre os resultados da operação DFI nas im-                  |    |

|     | plementações em modo pulsado e em modo de amplitude                                | 74 |

## Lista de Tabelas

| 2.1 | Parâmetros utilizados para o projeto da OPL                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 17 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.1 | Latências máximas (em ns) associadas ao processamento dos elementos de três diferentes técnicas AER (AB, WTA e NA) para um total $(X \cdot Y) = 50^2$ e $(X \cdot Y) = 100^2$ neurônios                                                                                                                                                                                                                                                                                                                           | 39 |

| 3.2 | Complexidade de <i>hardware</i> , com valores dados em transistores (ou em bits para o canal), envolvida com os elementos de três diferentes técnicas AER, AB ([33]), WTA ([34]) e NA ([35]). $X \cdot Y = 50^2$ e $100^2$                                                                                                                                                                                                                                                                                        |    |

| 3.3 | neurônios                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 41 |

| 3.4 | $X \cdot Y = 100^2$ . Comparativo das taxas máximas de transferência entre as técnicas AER proposta (NAP) e duas outras, AB e WTA. A técnica proposta atinge quase o dobro da taxa máxima de transferência da técnica AB e se aproximou do resultado produzido pela técnica WTA. Os valores de taxa máxima de transferência para as técnicas WTA e AB foram retirados de [32] e [34]. As condições de simulação impostas para o NAP foram semelhantes àquelas que produziram os resultados da técnica AB e da WTA | 48 |

| 4.1 | Caraterísticas da simulação elétrica do sistema AER proposto processando um estímulo em diagonal. Nesse caso a OPL foi desabilitada possibilitando a comunicação apenas pelo canal $On.$                                                                                                                                                                                                                                                                                                                          | 57 |

### Lista de Abreviaturas

$I_D$  Drain Current, p. 13

$I_F$  Forward Current, p. 13

$I_R$  Reverse Current, p. 13

$V_P$  Pinch-Off Voltage, p. 14

$V_T$  Threshold Voltage, p. 12

$i_D$  Normalized Drain Current, p. 13

$i_F$  Normalized Forward Current, p. 13

$i_R$  Normalized Reverse Current, p. 13

AB Árvore Binária, p. 31

BCS Boundary Contour System, p. 70

BP Bipole Grouping, p. 71

CD Células de Decisão, p. 32

CMOS Complementary Metal-Oxide-Semiconductor, p. 7

Cpd Cycles per Degree, p. 10

DFI Diffusive Filling-In, p. 4

DF Directional Filtering, p. 70

EKV Enz, Krummenacher, and Vittoz, p. 13

ER Event Representation, p. 19

EVS Early Visual System, p. 5

Enc Encoder Cell, p. 36

FD Fully Dedicated, p. 4

IC Inversion Coefficient, p. 13

IF Integrate-and-Fire, p. 19

IPL Inner Plexiform Layer, p. 5

LIF Leakage Integrate and Fire, p. 64

MOS Metal-Oxide-Semiconductor, p. 4

MRP Mecanismo de Redução de Probabilidade, p. 43

NAND Negative AND, p. 32

NAP Não Arbitrado Proposto, p. 48

NA Não Arbitrado, p. 39

OPL Outer Plexiform Layer, p. 5

RNA Redes Neurais Artificiais, p. 1

SA Shared Axons, p. 4

SC Spatial Competition, p. 71

SD Shared Dendrite, p. 78

SS Shared Synapse, p. 78

SoC System on Chip, p. 26

Spk/s Spikes por Segundo, p. 10

TDM Time-Division-Multiplexing, p. 20

WTA Winner Takes All, p. 32

## Capítulo 1

## Introdução

No sistema visual biológico a luz entra pelos olhos, a informação luminosa é convertida em um sinal elétrico, processada por um conjunto de camadas de neurônios na retina e é transmitida ao córtex visual por meio de um canal conhecido como nervo óptico. O estágio de processamento anterior ao córtex visual é conhecido como sistema visual precoce ou Early Vision System (EVS). Esse conjunto de camadas de processamento permite reduzir a informação redundante presente no sinal visual bem como alterar a representação da informação de níveis de intensidade para uma representação onde a informação está relacionada aos intervalos de tempos demarcados por uma sequência de eventos, pulsos elétricos, gerados pelos neurônios que estão conectados ao nervo óptico. O nervo óptico consiste de milhares de canais paralelos que conectam as saídas dos neurônios da última camada de processamento do EVS as entradas dos neurônios no córtex visual. No córtex visual circuitos corticais compostos por milhões de neurônios conectados por um número maior ainda de conexões sinápticas realizam diversas tarefas de processamento sobre esse sinal pulsado. Como exemplo, podemos citar o reconhecimento de padrões visuais e a estimativa da distância de objetos. O estudo dos circuitos corticais possibilita a compreensão de como o cérebro realiza tarefas de processamento de maneira paralela, distribuída e utilizando níveis muito baixos de energia. Cerca de 1% da energia consumida por sistemas convencionais de processamento para realizar uma tarefa equivalente [1], [2]. Esses estudos servem também de inspiração para o desenvolvimento de novos sistemas de processamento. Redes neurais artificiais (RNA) são exemplos de sistemas de processamento inspirados no funcionamento do cérebro. No estudo dos circuitos corticais experimentos sobre a estrutura fisiológica do cérebro são realizados, hipóteses são levantadas, modelos baseados nessas hipóteses são criados e simulações permitem que esses modelos sejam checados e compreendidos. O custo computacional necessário para a simulação de circuitos corticais, utilizando sistemas de processamento convencionais, se torna proibitivo à medida que esses modelos se tornam mais semelhantes aqueles encontrados na biologia [3]. A simula-

ção de modelos de circuitos corticais pode ser cerca de 9000 vezes mais lenta do que o processamento em tempo real realizado pelos circuitos corticais biológicos, caso os sinais de entrada e saída dos neurônios sejam considerados como sequências de pulsos que codificam a informação (modo pulsado ou spike-mode), como acontece na biologia [4]. As primeiras gerações de RNAs possuem sinais com valores escalares nas entradas e saídas dos neurônios (modo de amplitude) que representam as taxas com que os pulsos elétricos são transmitidos através da rede neural. Essa é uma estratégia para reduzir o custo computacional envolvido com as simulações das redes neurais visto que na época o poder computacional era muito limitado. Em estudos onde interessam as propriedades pulsadas dos neurônios o modo de amplitude não pode ser utilizado e o desenvolvimento de sistemas de processamento que fazem uso de arquiteturas de processamento semelhantes aquelas apresentadas pelo cérebro são imprescindíveis [5]. Esses sistemas de processamento dedicados contam com hardware específico que foge às arquiteturas tradicionalmente imaginadas por Turing e Neumann [6], [7] para os sistemas de computação que são utilizados nos dias atuais. Esse hardware específico segue uma arquitetura parecida com aquela que é apresentada pelos circuitos corticais biológicos, como por exemplo, o projeto SpiNNaker [8].

### 1.1 Motivações

A computação analógica, por explorar as propriedades físicas dos dispositivos semicondutores para realizar processamento, leva vantagem sobre a computação digital em relação à complexidade de hardware e o consumo de energia. Por exemplo, é muito mais econômico, em termo de hardware, representar uma quantidade a partir de um nível utilizando grandezas como corrente ou tensão, do que representar a mesma quantidade por um conjunto de sinais onde cada sinal é uma variável binária. Operações realizadas entre quantidades que são representadas por níveis podem ser realizadas em regimes de muito baixa corrente ou muito baixa tensão, evitando consumo de energia desnecessário [1]. Contudo, a computação analógica baseada na representação de quantidades por níveis é susceptível a ruído e ao descasamento no processo de fabricação. Na área de microeletrônica o descasamento no processo de fabricação indica o quanto as dimensões de transistores MOS iguais variam devido a imperfeições do material ao serem posicionados em locais diferentes. Por explorar propriedades físicas, que muitas vezes são fixas, sistemas analógicos de computação não são muito flexíveis à programação. Dessa maneira, criar sistemas de computação analógica que substituam os tradicionais computadores digitais [7] ainda representa um enorme desafio para os projetistas. Olhando por outro ponto de vista, os circuitos corticais biológicos realizam operações de processamento de maneira analógica, paralela, distribuída e ainda apresentam flexibilidade de programação (plasticidade neural) [1], [4]. O desenvolvimento de um sistema de processamento que realize computação analógica baseado no funcionamento do cérebro é uma motivação para o estudo dos circuitos corticais.

#### 1.2 Problemática

Apesar de toda uma expectativa por esses novos sistemas de computação estes estão longe de se tornarem realidade e não passam de um sonho futurista. No estágio atual da pesquisa existem outras preocupações. Uma dessas preocupações está relacionada a formas de se realizar o estudo dos circuitos corticais por meio de simulações. Como foi dito, esse estudo deve ser conduzido por meio de um hardware dedicado que permite simulações em modo pulsado. Previsões teóricas devem ser consideradas antes da implementação desse hardware dedicado. Essas previsões teóricas fornecem bases conclusivas sobre as especificações do projeto do hardware dedicado, como por exemplo, o tipo de neurônio a ser utilizado em determinado modelo do circuito cortical. Existem algumas formas de se fazer previsões teóricas sobre os circuitos corticais e assim obter resultados que mostram seu comportamento. O modo pulsado não pode ser substituído pelo modo de amplitude caso se esteja fazendo um estudo das propriedades pulsadas do circuito cortical. Contudo, é possível que os resultados de previsão teórica feitos em modo de amplitude tenham serventia para serem utilizados para dimensionamento do hardware dedicado [9], [10]. No modo de amplitude a sequência de pulsos nas entradas e na saída dos neurônios é associada a uma sequência de valores escalares que representam a taxa de disparo dos neurônios dentro de uma janela temporal. Também é possível utilizar computadores de muito alto desempenho [11], caso estes estejam disponíveis, para realizar essas previsões direto em modo pulsado. Existem casos onde às previsões não são consideradas, os detalhes de especificação do projeto são ignorados e o que é visto é um superdimensionamento no projeto do hardware dedicado [5]. Entre os três casos apresentados (o modo de amplitude, o uso de computadores de alto desempenho e o superdimensionamento do hardware dedicado), a opção mais acessível é o modo de amplitude. Utilizar o modo de amplitude, uma sequência de valores escalares representando um sinal composto por uma sequência de pulsos, é uma abordagem que desconsidera importantes características da dinâmica neural, como por exemplo, a influência dos pulsos do sinal (spikes) nos laços de realimentação, a influência dos spikes na combinação linear das entradas, o exato comportamento do neurônio logo após ele disparar e a influência do formato do *spike* na resposta do sistema. Assim, não se sabe ao certo se o modo de amplitude realmente pode fornecer resultados próximos àqueles que se obteriam caso pudéssemos utilizar sinais compostos por sequências de spikes nas entradas e saídas dos neurônios (modo pulsado) mesmo se quiséssemos usar esses dados para dimensionar o hardware dedicado. O desenvolvimento de hardware para o processamento pulsado não é trivial e muitos problemas surgem ao se tentar desenvolver esse tipo de dispositivo. Implementações em hardware envolvendo dimensões tão grandes, milhares de neurônios conectados por milhões de conexões sinápticas, podem não estar disponíveis caso uma topologia de projeto semelhante àquela apresentada pelo cérebro seja utilizada para implementar os circuitos corticais. A topologia que imita a utilizada pelo cérebro é conhecida como completamente dedicada (Fully Dedicated - FD). A topologia FD é aquela onde existe um dispositivo físico representando cada elemento a ser implementado do circuito cortical [4]. Por exemplo, para cada neurônio implementado em hardware existe um dispositivo MOS (Metal-Oxide-Semiconductor) que o representa. O mesmo se aplica às sinapses, dendritos e outros elementos da rede neural. Uma maneira de se contornar esse problema é utilizar topologias onde elementos da rede neural sejam compartilhados. Como por exemplo, o dispositivo físico que implementa um axônio pode ser utilizado por mais de um elemento físico que implementa um neurônio. A essa topologia chamamos de axônio compartilhado (Shared Axons - SA). Contudo, topologias como a SA são baseadas em troca de informação por multiplexação no tempo, o que causa atrasos aleatórios no sinal a ser transmitido. No caso de um sistema onde a informação está relacionada ao intervalo de tempo entre pulsos consecutivos, como é o caso dos circuitos neurais, esses atrasos distorcem a informação. A latência [12] é uma medida relacionada a distorção causada por esses atrasos aleatórios ao sinal. Saber como a latência inserida por topologias de redução da quantidade de circuitos (redução da complexidade de hardware) como a SA influenciam o comportamento de um dispositivo que implementa um circuito cortical é uma questão importante.

### 1.3 Objetivos

Nosso objetivo é desenvolver um diagrama esquemático de uma retina de silício que será composta pelos estágios de processamento do EVS e implementar o algoritmo do diffusive filling-in (DFI) em dois modos, em modo pulsado e em modo de amplitude. O DFI é um mecanismo do córtex visual biológico ligado à reconstrução de imagens [13]. Esse circuito cortical foi escolhido por ser simples o bastante para ser implementado tanto em modo de amplitude [14], como em modo pulsado [9]. Os dois modos de implementação possibilitarão responder se o modo de amplitude pode ser utilizado para gerar resultados de previsão teórica capazes de auxiliar no dimensionamento de um hardware dedicado. Para tornar os resultados obtidos com as simulações do algoritmo do DFI mais realistas iremos adotar uma abordagem de tratamento dos estímulos diferente daquela que é utilizada tradicionalmente a

partir de filtros de diferenças-de-gaussianas (Difference-of-Gaussians - DoG). Nessa abordagem a resposta da retina é aproximada por uma filtragem com filtros DoG. Na nossa abordagem utilizaremos o diagrama esquemático da retina para fazer esse tratamento. Um ruído característico da filtragem passa-banda espacial da retina é considerado no processamento, tornando a abordagem proposta mais realista. Esse ruído característico realça as diferenças entre as duas simulações e permite testar a previsão em modo de amplitude em condições mais adversas. No modelo elétrico da retina iremos introduzir um sistema de comunicação que utiliza topologia SA. Esse sistema de comunicação, que foi proposto nesse trabalho, apresenta índices de latência menores que os sistemas de comunicação apresentados tradicionalmente, mantendo a complexidade de hardware equivalente. Essa abordagem é importante porque permite avaliar os efeitos causados pela técnica de redução da complexidade de hardware que será utilizada.

### 1.4 Metodologia de Trabalho

No Cap. 2, faremos uma revisão sobre o sistema visual precoce ou Early Visual System (EVS). A partir dessa revisão iremos apresentar um modelo para cada camada de processamento do EVS, Outer Plexiform Layer (OPL), Inner Plexiform Layer (IPL) e camada das células ganglionares. Uma metodologia será proposta para projetar a camada da OPL, a partir de transistores MOS. Resultados sobre o funcionamento da metodologia de projeto da OPL e do funcionamento da IPL são apresentados. Os resultados mostram que tanto o modelo elétrico da OPL quanto o da IPL respondem de acordo com o esperado. No Cap. 3 é proposto um sistema de comunicação, utilizando topologia SA, que substitui o nervo óptico. Esse sistema de comunicação permite reduzir fisicamente as conexões feitas entre as saídas da retina e as entradas dos circuitos corticais do algoritmo DFI de  $n^2$  para  $\log_2(n)$ , apresentando níveis de latência menores que aqueles dos sistemas de comunicação utilizados tradicionalmente e mantendo a complexidade de hardware equivalente. São mostrados resultados relacionados a latência e a complexidade de hardware do sistema de comunicação. Esses resultados comprovam que o sistema de comunicação proposto apresenta latência menor que o sistema que costuma ser utilizado e uma complexidade de hardware equivalente. O diagrama esquemático da retina utilizando o sistema de comunicação proposto é apresentado no Cap. 4. A resposta ao impulso do diagrama esquemático da retina e exemplos de imagens reconstruídas são apresentados. No Cap. 5 introduziremos a ideia de processamento em modo pulsado e de como funciona a dinâmica neuronal. Apresentaremos um modelo do algoritmo DFI que será utilizado nesse trabalho. Faremos duas implementações do algoritmo DFI, uma em modo de amplitude [15] e outra em modo pulsado [9]. Mostraremos exemplos de utilização dessas implementações e o esquema de processamento utilizado por elas. Os resultados das simulações feitas com o modelo do algoritmo DFI são apresentados. Esses resultados mostram também que as previsões feitas em modo de amplitude são muito próximas as previsões feitas em modo pulsado apesar das distorções (latência e filtragem passa-banda espacial da retina) inseridas no sinal de estímulo utilizado como entrada do algoritmo DFI. No Cap. 6 concluímos que os resultados apresentados mostram que a metodologia de projeto para a OPL funciona, que o sistema de comunicação é capaz de substituir os sistemas tradicionalmente utilizados apresentando vantagens em relação a latência e a complexidade de hardware. Apresentamos indícios de que o modo de amplitude é capaz de fazer previsões próximas àquelas que seriam feitas utilizando o modo pulsado para o DFI.

## Capítulo 2

## O EVS e os Estímulos para o DFI

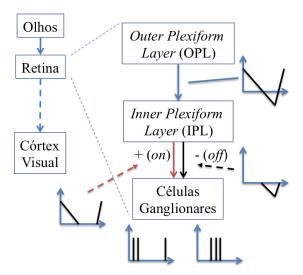

Serão introduzidos a seguir os conceitos básicos que permitirão o desenvolvimento do modelo elétrico da retina (diagrama esquemático), avaliado para implementação CMOS (Complementary Metal-Oxide-Semiconductor) [16]. O modelo elétrico da retina possui três estágios de processamento, a OPL, a IPL e a camada das células ganglionares. Um diagrama em bloco desse esquema, que também é conhecido como EVS, pode ser visto na Fig. 2.1.

Figura 2.1: Diagrama em blocos do EVS. É apresentada a OPL, a IPL, a camada de células ganglionares e os respectivos sinais em suas entradas e saídas.

O sistema visual biológico possui ainda um estágio de transmissão de informações da retina até o córtex, conhecido como nervo óptico. Nesse capítulo serão apresentados o modelo elétrico da OPL [16], o modelo elétrico da IPL (sistema retificador [17]), e o modelo das células ganglionares [16]. Falaremos sobre o sistema de comunicação, que corresponde ao nervo óptico, no Cap. 3. O sistema de comunicação é baseado na topologia SA e permite redução na complexidade de hardware para uma futura implementação do modelo elétrico da retina em silício. O diagrama esquemático

da retina desenvolvido será utilizado para auxiliar no processamento dos estímulos que serão utilizados como entradas para o DFI. No Cap. 4 será apresentada uma discussão sobre os motivos que mostram que essa abordagem é mais realista do que a que tradicionalmente é utilizada com filtros DoG. Serão introduzidos os fundamentos teóricos apresentando o modelo elétrico da OPL.

### 2.1 Modelo para a OPL

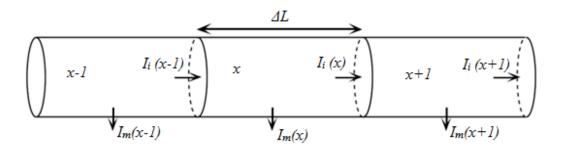

A OPL biológica é uma camada de processamento do EVS que é formada por dois tipos de neurônios, os fotorreceptores e as células horizontais. Os fotorreceptores transduzem a intensidade luminosa da informação visual em sinal elétrico. Estudos fisiológicos revelam que os fotorreceptores são interconectados por meio de junções elétricas resistivas que permitem a difusão da corrente elétrica produzida em um dos fotorreceptores para os seus respectivos vizinhos [18]. O mesmo conceito se aplica às células horizontais. Essa estrutura composta de neurônios conectados por conexões resistivas permite espalhamento lateral de corrente tanto na rede de fotorreceptores como na rede das células horizontais. Existem conexões entre os fotorreceptores e as células horizontais que permitem difusão de corrente elétrica entre esses dois grupos de neurônios [19], [20]. Essas interações permitem uma filtragem passa-banda no domínio do espaço e do tempo do sinal transduzido que ocorre nesse estágio. Essa é uma estratégia biológica que visa reduzir a informação redundante no sinal visual. O modelo da OPL apresentado em [21] associa as difusões de corrente que ocorrem entre os fotorreceptores ou entre células horizontais na OPL as interações elétricas que ocorrem entre os elementos infinitesimais de um cabo elétrico. A Fig. 2.2 mostra um exemplo de um cabo elétrico e as correntes elétricas conduzidas por ele.

Figura 2.2: Em um cabo dividido em elementos infinitesimais (x), de comprimento  $\Delta L$ , existe uma corrente que flui horizontalmente pelo cabo  $(I_i(x))$  e uma corrente que é conduzida verticalmente pelo elemento infinitesimal  $(I_m(x))$ .

No cabo elétrico os elementos infinitesimais estão divididos horizontalmente e x representa a posição na qual o elemento infinitesimal se encontra. A corrente

lateral entre os elementos infinitesimais é indicada pelo símbolo  $I_i$  e a corrente que é conduzida verticalmente por cada elemento infinitesimal é indicada pelo símbolo  $I_m$ . O modelo elétrico desse cabo é mostrado na Fig. 2.3. Os elementos infinitesimais do cabo são formados por capacitâncias  $(C_m)$  em paralelo com uma condutância  $(g_m)$ . Esses elementos são conectados entre si por meio de resistores horizontais  $(R_i)$  permitindo o espalhamento lateral de corrente.  $V_i$  é uma tensão associada ao elemento infinitesimal do cabo. I(x) é a corrente que flui através dos elementos infinitesimais de condutância  $g_m$ .

Figura 2.3: Os componentes do modelo elétrico de um cabo são apresentados. Os elementos infinitesimais do cabo (capacitâncias e condutâncias) são conectados a partir de resistores  $(R_i)$ .

Como o modelo elétrico de um neurônio é um capacitor e uma condutância conectados em paralelo [21], [22] foi possível associar o modelo elétrico do elemento infinitesimal do cabo ao modelo do neurônio [23]. É possível vincular as conexões resistivas que permitem interação entre os neurônios na OPL biológica aos elementos resistivos que aparecem no modelo elétrico do cabo. Após essas duas associações é possível comparar o modelo elétrico do cabo a um conjunto de neurônios da OPL interconectados lateralmente por meio de junções elétricas resistivas. Apresentadas essas considerações seguiremos com a descrição do comportamento do modelo da rede de fotorreceptores e da rede de células horizontais por meio da Eq. (2.1), equação que descreve o comportamento de um cabo elétrico.

$$V_i(x,t) = \lambda^2 \cdot \frac{\partial^2 V_i(x,t)}{\partial x^2} - \tau \cdot \frac{\partial V_i(x,t)}{\partial t}$$

(2.1)

A Eq. (2.1) é uma variação da equação do cabo elétrico utilizada em [23] com  $\lambda^2 = \frac{1}{R_i \cdot g_m(x)}$  e  $\tau = \frac{c_m}{g_m(x)}$ . Ao ser inserido um estímulo  $I_p(x,t)$  na posição x do cabo e considerando que esse estímulo é um impulso no espaço e no tempo, temos que a Eq. (2.1) se torna:

$$V_i(x,t) = \lambda^2 \cdot \frac{\partial^2 V_i(x,t)}{\partial x^2} - \tau \cdot \frac{\partial V_i(x,t)}{\partial t} + \frac{1}{g_m} \cdot I_p(x,t)$$

(2.2)

A transformada de Fourier de  $V_i(x,t)$ , na Eq. (2.2), pode ser descrita como sendo  $V_i(u,w)$ , na Eq. (2.3). Onde  $i=\sqrt{-1}$ .

$$V_i(u,w) = \frac{I_p(u,w)}{g_m} \cdot \frac{1}{\lambda^2 \cdot u^2 + \tau \cdot i \cdot w + 1}$$

$$(2.3)$$

A resposta ao impulso do modelo elétrico do cabo é mostrado na Eq. (2.1). Assim foi possível modelar o comportamento das redes de fotorreceptores e de células horizontais utilizando a Eq. (2.1). No sistema visual cada célula horizontal recebe do fotorreceptor de mesma posição uma corrente proporcional a sua atividade. Por sua vez, cada célula horizontal drena um valor de corrente proporcional à sua atividade desse mesmo fotorreceptor. Será assumido aqui que  $V_c(x,t)$  é o sinal que corresponde a atividade dos fotorreceptores e que  $V_h(x,t)$  é o sinal que corresponde a atividade das células horizontais. Em termos de modelo é possível descrever esse comportamento a partir do sistema de equações apresentado na Eq. (2.4).

$$\begin{cases} V_c(u, w) = \frac{I_p(u, w) - I_h(u, w)}{g_{m_c}} \cdot \frac{1}{\lambda_c^2 \cdot u^2 + \tau_c \cdot i \cdot w + 1}, \\ V_h(u, w) = \frac{I_c(u, w)}{g_{m_h}} \cdot \frac{1}{\lambda_h^2 \cdot u^2 + \tau_h \cdot i \cdot w + 1}, \end{cases}$$

(2.4)

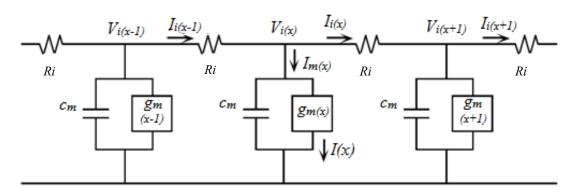

$I_c$  é uma corrente proporcional a  $V_c$  e  $I_h$  é uma corrente proporcional a  $V_h$ . Em [16] foi proposto um modelo elétrico da OPL, Fig. 2.4, baseado no modelo apresentado na Eq. (2.4).

Utilizando os mesmos procedimentos que possibilitaram escrever o sistema de equações apresentado na Eq. (2.4) foi possível descrever o sistema de equações apresentado na Eq. (2.5) para o modelo apresentado na Fig. 2.4.