### MÉTODOS PARA APRIMORAR O PROJETO E O LAYOUT DE FILTROS ANALÓGICOS EM CIRCUITOS INTEGRADOS CMOS

Carlos Fernando Teodósio Soares

Tese de Doutorado apresentada ao Programa de Pós-graduação em Engenharia Elétrica, COPPE, da Universidade Federal do Rio de Janeiro, como parte dos requisitos necessários à obtenção do título de Doutor em Engenharia Elétrica.

Orientador: Antonio Petraglia

Rio de Janeiro Janeiro de 2009

# MÉTODOS PARA APRIMORAR O PROJETO E O LAYOUT DE FILTROS ANALÓGICOS EM CIRCUITOS INTEGRADOS CMOS

#### Carlos Fernando Teodósio Soares

TESE SUBMETIDA AO CORPO DOCENTE DO INSTITUTO ALBERTO LUIZ COIMBRA DE PÓS-GRADUAÇÃO E PESQUISA DE ENGENHARIA (COPPE) DA UNIVERSIDADE FEDERAL DO RIO DE JANEIRO COMO PARTE DOS REQUISITOS NECESSÁRIOS PARA A OBTENÇÃO DO GRAU DE DOUTOR EM CIÊNCIAS EM ENGENHARIA ELÉTRICA.

| Aprovada por: |                                                      |

|---------------|------------------------------------------------------|

|               |                                                      |

|               | Prof. Antonio Petraglia, Ph.D.                       |

|               |                                                      |

|               | Prof. Fernando Antônio Pinto Barúqui, D.Sc.          |

|               | Prof. Antonio Carneiro de Mesquita Filho, Dr.d'État  |

|               | 1 101. Antoino Carneiro de Mesquita Finio, Dr.d Etat |

|               | Prof. Jader Alves de Lima Filho, D.Sc.               |

|               |                                                      |

|               | Prof. Jacques Szczupak, Ph D                         |

Soares, Carlos Fernando Teodósio

Métodos para Aprimorar o Projeto e o Layout de Filtros Analógicos em Circuitos Integrados CMOS/Carlos Fernando Teodósio Soares. — Rio de Janeiro: UFRJ/COPPE, 2009.

VIII, 149 p. 29,7cm.

Orientador: Antonio Petraglia

Tese (doutorado) – UFRJ/COPPE/Programa de Engenharia Elétrica, 2009.

Referências Bibliográficas: p. 138 – 149.

Filtros a Capacitores Chaveados.

Filtros Gm Algoritmos Genéticos.

Simulated Annealing.

Petraglia, Antonio. II. Universidade Federal do Rio de Janeiro, COPPE, Programa de Engenharia Elétrica. III.

Título.

## AGRADECIMENTOS

Agradeço primeiramente à Deus pelos dons concedidos à minha pessoa, os quais me levaram a seguir a carreira acadêmica em engenharia eletrônica, e pela ajuda nos momentos em que a minha limitada capacidade humana se mostrava impotente.

Agradeço à minha família pelo apoio, incentivo e, principalmente, pela compreensão nos constantes momentos em que estive ausente devido aos estudos e afazeres do curso de doutorado.

Agradeço ao meu orientador Prof. Antonio Petraglia por toda a sua ajuda, compreensão e incentivo ao longo desses cinco anos de mestrado e doutorado, cuja orientação foi muito além das simples atividades de pesquisa acadêmica.

Ao Prof. Antonio Carneiro de Mesquita Filho pelos conhecimentos transmitidos nas disciplinas que cursei ao longo do doutorado e pelas valiosas sugestões e discussões sobre a implementação do algoritmo genético para a aproximação das razões de capacitâncias. Ao Prof. Fernando Antônio Pinto Barúqui pela constante disponibilidade para conversar e discutir idéias sobre o projeto do filtro contínuo.

Aos colegas e professores do Laboratório de Eletrônica de Potência e do Laboratório de Processamento Analógico e Digital de Sinais, com os quais convivi durante todo esse tempo de curso, e que estarão permanentemente presentes na minha memória.

Ao Conselho Nacional de Desenvolvimento Científico e Tecnológico (CNPq) pela bolsa de doutorado paga a mim durante todo o curso de doutorado, sem a qual eu não conseguiria chegar até esta pequisa de tese.

Aos alunos do Departamento de Engenharia Eletrônica e de Computação que tiveram aula comigo da disciplina Eletrônica II, com os quais eu aprendi tanto quanto ensinei.

À Universidade Federal do Rio de Janeiro pela excelência de ensino que proporcionou a mim e a qualidade da formação profissional que hoje conquisto.

E, finalmente, dedico esta tese a todos aqueles, famosos ou anônimos, que valorizam o conhecimento e que trabalham para difundí-lo e empregá-lo de forma responsável na melhoria da qualidade de vida da humanidade.

Resumo da Tese apresentada à COPPE/UFRJ como parte dos requisitos necessários para a obtenção do grau de Doutor em Ciências (D.Sc.)

# MÉTODOS PARA APRIMORAR O PROJETO E O LAYOUT DE FILTROS ANALÓGICOS EM CIRCUITOS INTEGRADOS CMOS

Carlos Fernando Teodósio Soares

Janeiro/2009

Orientador: Antonio Petraglia

Programa: Engenharia Elétrica

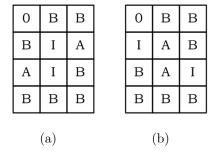

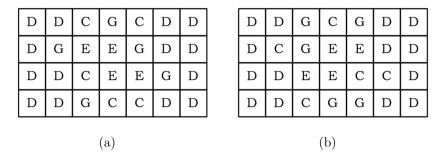

Casamento de capacitores é uma das questões mais críticas no projeto de filtros a capacitores chaveados em circuitos integrados CMOS. De acordo com a literatura, a técnica mais bem sucedida para realizar o casamento de capacitores consiste em implementar cada capacitor por um número inteiro de capacitores unitários idênticos e arranjá-los no layout empregando uma geometria com centróide comum. Entretanto, tais técnicas não são aplicáveis em geral, pois nem sempre todas as capacitâncias de um filtro podem ser expressas por um múltiplo inteiro de uma mesma capacitância unitária e, mesmo assim, dependendo do número de capacitores unitários, não é sempre possível obter um arranjo com centróide comum. Com o objetivo de solucionar tais dificuldades, um método, baseado em algoritmos genéticos, é proposto para aproximar por números racionais as razões de capacitâncias de um filtro a capacitores chaveados de maneira ótima. O presente trabalho também propõe uma metodologia, baseada em simulated annealing, para se otimizar o layout de capacitores unitários em um circuito integrado. Além disso, o projeto de filtros contínuos Gm-C também é considerado neste trabalho, com a proposta de uma topologia de amplificador operacional de transcondutância com baixa distorção para uma ampla faixa da tensão diferencial de entrada, adequada para filtros na faixa de dezenas de quilohertz. Análises de Monte Carlo usando o simulador Spectre foram realizadas para verificar a robustez dos circuitos a descasamentos e a variações nos parâmetros do processo de fabricação.

Abstract of Thesis presented to COPPE/UFRJ as a partial fulfillment of the requirements for the degree of Doctor of Science (D.Sc.)

# METHODS TO IMPROVE THE DESIGN AND LAYOUT OF CMOS ANALOG INTEGRATED CIRCUITS

Carlos Fernando Teodósio Soares

January/2009

Advisor: Antonio Petraglia

Department: Electrical Engineering

Capacitance matching is a critical issue in the design of switched-capacitor filters. According to previous works, the most successful technique employed to match integrated capacitors consists in implementing each filter capacitor by an integer number of identical unit capacitors in parallel, arranged in the layout using common centroid geometry. However, this technique is not applicable in general, because all filter capacitances should be expressed as integer multiples of the same unit capacitance. Furthermore, depending on the number of unit capacitors, an arrangement with a common centroid is impossible to be achieved. In order to address these difficulties, a method based on genetic algorithms is proposed to find the optimal approximation by integer ratios of the capacitance ratios in a switched-capacitor filter. This work also proposes a computational method based on simulated annealing to optimize the arrangement of unit capacitors in the layout. In addition, the design of continuoustime Gm-C filters is also considered in this work. An operational transconductance amplifier topology with low distortion for a large input voltage swing is proposed, which is suitable for filters with cutt-off frequencies at dozens of kilohertz. Monte Carlo analyses using Spectre simulator were carried out to verify the robustness of the developed circuits to mismatches and variations in the fabrication process parameters.

vi

# Sumário

| Ι   | Intr  | odução  | )                                          | 1  |

|-----|-------|---------|--------------------------------------------|----|

|     | I.1   | Aproxi  | imação das Razões de Capacitâncias         | 2  |

|     | I.2   | Layout  | t das Matrizes de Capacitores Unitários    | 5  |

|     | I.3   | Filtro  | Contínuo no Tempo                          | 8  |

| II  | Apr   | oxima   | ção das Razões de Capacitâncias            | 11 |

|     | II.1  | Filtros | a Capacitores Chaveados                    | 12 |

|     |       | II.1.1  | Simulação de Rede Ladder                   | 12 |

|     |       | II.1.2  | Cascata de Biquads                         | 23 |

|     | II.2  | Métod   | o de Aproximação                           | 25 |

|     |       | II.2.1  | Codificação dos Cromossomos                | 27 |

|     |       | II.2.2  | Função Custo                               | 34 |

|     |       | II.2.3  | População Inicial                          | 36 |

|     |       | II.2.4  | Seleção e Cruzamento                       | 37 |

|     |       | II.2.5  | Mutações                                   | 38 |

|     |       | II.2.6  | Elitismo                                   | 38 |

|     |       | II.2.7  | Critério de Parada                         | 38 |

|     | II.3  | Result  | ados                                       | 38 |

|     |       | II.3.1  | Filtro Obtido por Simulação de Rede Ladder | 38 |

|     |       | II.3.2  | Filtro com Cascata de Biquads              | 40 |

| III | Otir  | nizaçã  | o do Layout dos Capacitores                | 44 |

|     | III.1 | Aprese  | entação do Problema                        | 44 |

|     | III.2 | Métod   | o Proposto                                 | 53 |

|     |       | III.2.1 | Estrutura de Dados Adotada                 | 53 |

|     |       | III.2.2 | Restrição do Problema                      | 54 |

|     |       | III.2.3 | Função Custo                               | 55 |

|     |       | III.2.4 | Algoritmo de Otimização                    | 57 |

|     | III.3 |         | ados Obtidos                               | 62 |

|     |       |         | Exemplos Ilustrativos                      | 62 |

|     |       |         | Layout do Filtro Ladder                    | 66 |

|              |       | III.3.3 Layout do Filtro Cascata de Biquads             | 72  |

|--------------|-------|---------------------------------------------------------|-----|

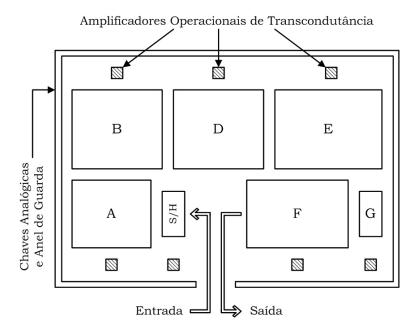

| IV           | Filt  | ro Gm-C Anti-aliasing                                   | 77  |

|              | IV.1  | Projeto Preliminar do Filtro Gm-C                       | 78  |

|              | IV.2  | Amplificador Operacional de Transcondutância            | 82  |

|              |       | IV.2.1 Revisão Bibliográfica                            | 82  |

|              |       | IV.2.2 Topologia Proposta                               | 90  |

|              |       | IV.2.3 Controle de Modo Comum                           | 93  |

|              |       | IV.2.4 Projeto do OTA                                   | 97  |

|              | IV.3  | Simulações                                              | 107 |

|              |       | IV.3.1 Resultados Obtidos para o Atenuador MOS          | 108 |

|              |       | IV.3.2 Resultados Obtidos para o OTA                    | 115 |

|              |       | IV.3.3 Resultados Obtidos para o Controle de Modo Comum | 122 |

|              |       | IV.3.4 Resultados Obtidos para o Filtro Gm-C            | 125 |

| $\mathbf{V}$ | Con   | nclusão                                                 | 134 |

|              | V.1   | Aproximação das Razões de Capacitâncias                 | 134 |

|              | V.2   | Layout das Matrizes de Capacitores                      | 135 |

|              | V.3   | Filtro OTA-C Contínuo no Tempo                          | 136 |

| Re           | eferê | ncias Bibliográficas                                    | 138 |

## CAPÍTULO I

# Introdução

Atualmente, devido à enorme concorrência entre as empresas que realizam projetos de circuitos integrados, há a necessidade de se minimizar o tempo de desenvolvimento dos projetos com o objetivo de lançar no mercado um produto novo antes dos demais concorrentes. Quanto maior for o intervalo de tempo entre a chegada do primeiro produto ao mercado e o lançamento de um similar pela concorrência, maiores serão os ganhos de capital da empresa pioneira. Se, por outro lado, uma empresa não conseguir lançar um produto novo antes da concorrência, os ganhos serão menores e maior será o tempo necessário para compensar os custos de desenvolvimento do projeto.

No caso de circuitos integrados digitais, existem atualmente diversas ferramentas de CAD (*Computer Aided Design*) capazes de realizar automaticamente o projeto de circuitos com elevado nível de complexidade, partindo de um código escrito em uma linguagem de descrição de hardware — como, por exemplo, VHDL e Verilog.

Por outro lado, no caso de circuitos integrados analógicos, ainda não é possível atingir o mesmo grau de automatização verificado no projeto de sistemas digitais. Isso ocorre principalmente porque o projeto de circuitos analógicos envolve muito mais parâmetros de desempenho que o projeto de sistemas digitais. Enquanto neste último tipo de projeto o foco está basicamente na elaboração de funções lógicas e na otimização dos atrasos e tempos de processamento, os projetos analógicos também envolvem questões como resposta em freqüência, estabilidade, ruído, casamento entre componentes e linearidade.

Para se conseguir um bom casamento entre componentes de um circuito integrado, por exemplo, o projetista de *layout* precisa empregar diferentes técnicas no arranjo desses componentes. Essa tarefa normalmente consome bastante tempo do projetista, elevando o custo de desenvolvimento e retardando o lançamento de um produto novo no mercado. Por essa razão, muitas empresas não estão dispostas a

pagar por esse custo nos casos em que o casamento entre componentes não é um fator extremamente crítico para o projeto.

Por essa razão, um dos objetivos da presente pesquisa de tese é justamente a proposta de metodologias para automatizar as tarefas relacionadas ao casamento de componentes em circuitos integrados. Neste trabalho, o foco será o projeto de filtros analógicos, especialmente filtros a capacitores chaveados, cujo desempenho depende bastante do casamento entre os capacitores do filtro.

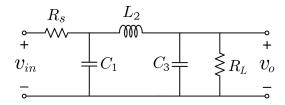

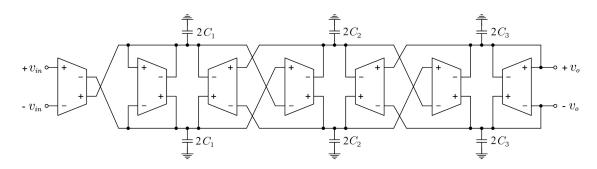

Além de filtros a capacitores chaveados, o presente trabalho também abordará o projeto de filtros OTA-C contínuos no tempo, os quais são freqüentemente empregados como filtros anti-aliasing para sistemas discretos no tempo — como os próprios filtros a capacitores chaveados ou filtros digitais. O objetivo é propor uma topologia de amplificador operacional de transcondutância (OTA) para aprimorar a linearidade e permitir a implementação de filtros OTA-C na faixa de dezenas de kilohertz, sem a necessidade de capacitores exageradamente grandes para a construção em circuito integrado.

Nas próximas seções, todas as propostas desta pesquisa de tese são descritas resumidamente. Os detalhes e os resultados obtidos são apresentados nos demais capítulos deste texto.

## I.1 - Aproximação das Razões de Capacitâncias

Filtros a capacitores chaveados tornaram-se populares entre os projetistas de circuitos integrados analógicos graças, principalmente, a duas características. A primeira é a possibilidade de se implementar filtros com pólos em baixas freqüências sem precisar de componentes passivos proibitivamente grandes, como capacitores e resistores. A segunda é a acurácia com que uma função de transferência pode ser implementada utilizando-se essa técnica, sem a necessidade de incluir qualquer tipo de sistema de calibração ou de sintonia automática [1,2].

Nos processos de fabricação de circuitos integrados CMOS, não é possível a implementação de capacitores com valores absolutos de capacitância bem precisos. Em geral, a maioria dos processos são capazes de implementar capacitores com tolerância de cerca de 20 a 40% [2]. Como os coeficientes da função de transferência de filtros contínuos no tempo dependem diretamente dos valores absolutos de capacitâncias, resistências, transcondutâncias e indutâncias, há a necessidade de algum tipo de calibração ou de sintonia automática para garantir uma resposta em freqüência com aceitável confiabilidade [3].

Por outro lado, a grande vantagem dos processos de fabricação de circuitos integrados é a capacidade de fabricar elementos muito bem casados. Dessa forma, valores relativos de capacitâncias podem ser perfeitamente implementados com tolerâncias

de até 0,1% [2], desde que técnicas adequadas de *layout* sejam adotadas pelo projetista [4–6]. Assim, mesmo que variações dos parâmetros do processo de fabricação afetem os valores absolutos dos capacitores, esses efeitos afetarão, na média, todos os capacitores de forma bastante semelhante, mantendo os valores relativos praticamente inalterados. Como os coeficientes de filtros a capacitores chaveados dependem exclusivamente de razões de capacitâncias [1], ou seja, valores relativos, as funções de transferência de tais filtros podem ser implementadas em processos CMOS com aceitável acurácia, sem a necessidade de calibração ou de sintonia automática.

Consequentemente, a acurácia da resposta em frequência de um filtro a capacitores chaveados dependerá diretamente do esforço empregado pelo projetista em usar as técnicas de *layout* adequadas para obter o melhor casamento possível entre os capacitores que compõem o filtro. Em circuitos integrados CMOS, os capacitores mais lineares são aqueles implementados com duas placas de material condutor metal ou silício policristalino — separadas por um dielétrico de óxido de silício. A capacitância desses dispositivos depende da área das placas, assim como de seus perímetros — devido ao efeito de franja do campo elétrico nas bordas das placas. Sendo assim, para casar dois capacitores, o projetista deve se preocupar em casar tanto a área, como também o perímetro de suas placas. De acordo com a literatura, a técnica mais conhecida e eficiente emprega capacitores idênticos em paralelo denominados capacitores unitários — para implementar cada um dos capacitores que devem ser muito bem casados [5, 7, 8]. Como exemplo, considere a razão de capacitores  $C_1/C_2 = 3/4$ . Nesse caso,  $C_1$  será composto por três capacitores unitários em paralelo, enquanto que  $C_2$  será composto por quatro. Assim, tanto área quanto perímetro estarão casados, formando a razão desejada.

Entretanto, em geral, os coeficientes das funções de transferência de filtros a capacitores chaveados não são números racionais, como mostrado no exemplo acima. Isso impede que a estratégia de se empregar capacitores unitários idênticos em paralelo seja diretamente aplicada ao caso geral. Em alguns textos [8], recomenda-se utilizar, juntamente com os unitários, alguns capacitores com tamanhos diferentes, de tal forma que as razões de capacitâncias que não são números racionais sejam satisfeitas. Uma outra estratégia seria aproximar cada razão de capacitâncias do filtro por um número racional, permitindo o emprego de capacitores unitários idênticos. A desvantagem da primeira abordagem é a necessidade de se incluir capacitores diferentes, que comprometem o casamento e dificultam o layout. Já a segunda abordagem tem a desvantagem de que as aproximações por números racionais acarretarão em erros na resposta em freqüência do filtro. Entretanto, como é possível aproximar qualquer número real por um número racional a partir de uma especificação de erro tolerável, as razões de capacitores podem ser aproximadas de forma que os erros produzidos na resposta em freqüência do filtro sejam aceitáveis.

Neste ponto da discussão, é importante mencionar que quanto menor for o erro especificado na aproximação de um número real por um racional, maiores serão os inteiros que aparecerão no numerador e no denominador. No caso da aproximação de razões de capacitores, isso representa um maior número de capacitores unitários em paralelo para implementar cada capacitor da razão, o que aumenta a área ocupada pelo filtro no circuito integrado e eleva o custo de fabricação. Para ilustrar essa situação, considere, por exemplo, a razão  $C_3/C_4=0,4376$ . Essa razão pode ser aproximada por  $C_3/C_4\approx 4/9=0,4444$ , com um erro de 1,56%. Entretanto, essa mesma razão também pode ser aproximada por  $C_3/C_4\approx 7/16=0,4375$ , com um erro de 0,023%. A primeira aproximação requer quatro capacitores unitários para a implementação de  $C_3$  e nove para  $C_4$ , levando a treze no total. Já a segunda aproximação, que produz um erro significativamente menor, requer um total de vinte e três capacitores unitários, o que ocuparia quase o dobro da área em um circuito integrado. Isso significa que há uma relação de compromisso entre precisão e área ocupada.

Portanto, o objetivo é encontrar os números racionais que aproximem todas as razões de capacitâncias de um filtro a capacitores chaveados, onde os numeradores e denominadores de cada razão sejam os menores inteiros possíveis, tais que os erros na resposta em frequência do filtro estejam dentro de uma tolerância especificada. Esta situação se assemelha ao problema de quantização em um filtro digital, onde os coeficientes reais da função de transferência do filtro devem ser representados por palavras binárias com precisão finita [9–13]. Nesse problema de quantização, a solução que produz o menor erro na resposta em freqüência do filtro digital não é necessariamente o simples arredondamento dos coeficientes originais [13]. Entretanto, o problema de quantização dos coeficientes de um filtro digital é essencialmente diferente do problema envolvendo as razões de capacitâncias. No primeiro, a precisão com que cada coeficiente é implementado está fixa, e o objetivo é minimizar o erro produzido na resposta em frequência. Já no segundo, a precisão com que os coeficientes serão implementados é arbitrária, dependendo apenas de quão grandes serão os números inteiros utilizados nas razões, e o objetivo é justamente encontrar as razões com os menores inteiros possíveis, tais que os erros na resposta em frequência sejam aceitáveis.

Em [14] e [15] as aproximações das razões de capacitâncias foram realizadas através de um método de busca determinístico, com o objetivo de minimizar o máximo erro na resposta em freqüência do filtro. No entanto, o método não tinha a preocupação em minimizar o número de capacitores unitários. Em [16], um método de otimização discreta, mais eficiente que o método de busca utilizado nos dois trabalhos anteriores, foi aplicado separadamente a cada seção de um filtro implementado através de uma cascata de seções biquadráticas (biquads). Todavia, o método serve

apenas para o caso específico de filtros implementados com cascata de biquads, e a interação entre seções não é levada em consideração durante a otimização. Tal interação permite que o erro de aproximação de uma seção possa ser cancelado pelo erro de uma outra seção pertencente à mesma cascata, reduzindo o erro total e relaxando a tolerância com que algumas razões de capacitâncias devem ser aproximadas. Infelizmente, a complexidade do método de aproximação proposto em [16] é altamente influenciada pelo número de capacitores do circuito. Essa característica o torna bastante inadequado para ser aplicado ao filtro inteiro, ao invés de ficar restrito a cada seção biquadrática separadamente. Em [17, 18] é apresentado um método que aproxima cada uma das razões de capacitâncias, separadamente, dada uma tolerância determinada através da sensibilidade do filtro. Apesar de ser um método computacionalmente bastante eficiente, as soluções encontradas não são ótimas, justamente pelo fato do método não levar em consideração a interação entre os erros de aproximação de todas as razões de capacitâncias sobre a resposta em freqüência do filtro. A sensibilidade do filtro também foi utilizada em [19] para resolver o problema de quantização dos coeficientes de filtros digitais.

No presente trabalho, um novo método é proposto para aproximar as razões de capacitâncias de um filtro a capacitores chaveados. O objetivo é minimizar a área ocupada pelos capacitores unitários que serão empregados na implementação das razões aproximadas, mantendo os erros na resposta em freqüência aceitáveis. Para isso, um algoritmo genético é adotado como método de busca para encontrar a solução ótima para esse problema.

Algoritmos genéticos são algoritmos de busca baseados no mecanismo de seleção natural e na evolução das espécies vivas, produzindo indivíduos cada vez melhores a cada geração, através de processos como seleção, cruzamentos e mutações. A grande vantagem desses algoritmos é a capacidade de lidar com problemas de otimização discreta, não lineares e com vários mínimos locais [20]. Em [13], por exemplo, um algoritmo genético foi empregado com sucesso na busca de uma solução para o problema de quantização dos coeficientes de um filtro digital.

No Capítulo II, é apresentada a implementação do método de aproximação das razões de capacitâncias empregando algoritmos genéticos. O método é, então, aplicado a dois projetos de filtros a capacitores chaveados para comprovar a sua eficácia.

### I.2 - Layout das Matrizes de Capacitores Unitários

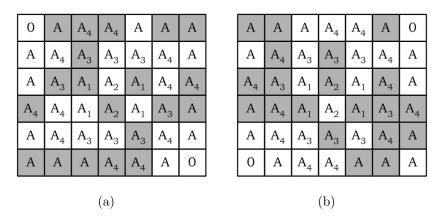

Conforme mencionado na seção anterior, a acurácia com que as razões de capacitâncias são implementadas pode ser melhorada se forem empregadas técnicas de *layout* adequadas. De acordo com a literatura, o casamento de capacitores MOS está sujeito a duas classes de erros [7,21,22]:

• Erros Aleatórios — São erros que ocorrem de forma imprevisível em dispositivos de circuitos integrados. Como são aleatórios, não podem ser corrigidos através de técnicas de layout. Portanto, os erros aleatórios representam a maior limitação da máxima acurácia que se pode obter em uma determinada tecnologia. Exemplos mais comuns de erros dessa natureza em capacitores MOS são: irregularidades nas bordas das placas que compõem os capacitores, variações aleatórias na espessura do óxido devido à rugosidade do material e flutuações na permissividade elétrica do óxido.

• Erros Sistemáticos — São erros decorrentes do modo como os dispositivos são implementados em um circuito integrado. Tais erros podem ser satisfatoriamente atenuados através de técnicas de layout adequadas. Exemplos de erros dessa natureza são: descasamentos nas razões dos perímetros, efeitos de proximidade dos dispositivos, capacitâncias parasitas nas interconexões, descasamentos nas interconexões e gradientes de temperatura e de espessura do óxido.

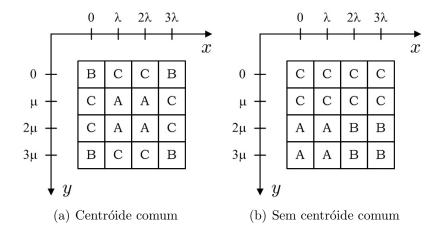

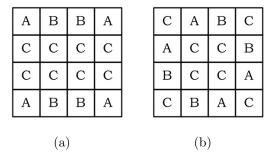

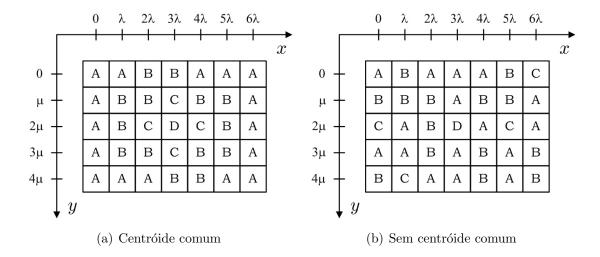

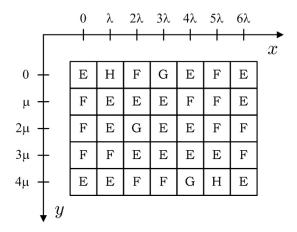

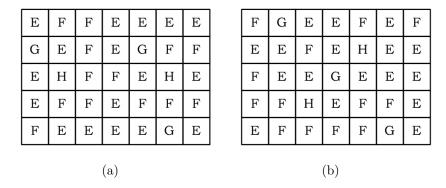

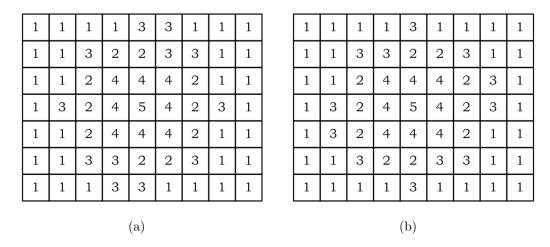

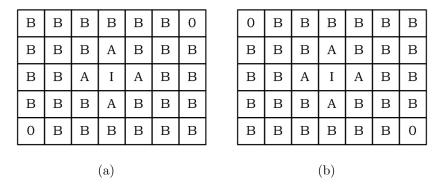

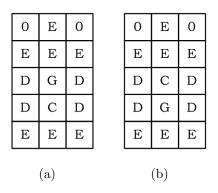

Em [7], é apresentado um estudo dos erros sistemáticos de casamento entre capacitores implementados em circuitos integrados MOS. Com base nos estudos desse trabalho, foram elaboradas algumas regras de layout para atenuar os efeitos de erros sistemáticos. Entre elas, recomenda-se o emprego de capacitores unitários idênticos a fim de se casar tanto área como perímetro. Caso sejam necessários capacitores com dimensões diferentes dos demais unitários, os autores recomendam que estes devam ter dimensões o mais próximas possível dos unitários. Além disso, os capacitores unitários devem ser posicionados no layout da forma mais simétrica possível. De preferência, empregando arranjos do tipo centróide comum, onde capacitores unitários pertencentes ao mesmo capacitor são dispostos simetricamente em relação ao centro da matriz de capacitores. Com esse arranjo, os centróides — também conhecidos como centros de massa — de todos os grupos de capacitores devem ser coincidentes, ou seja, comuns. Em [23], foram estudados diferentes posicionamentos simétricos de dispositivos MOS em um layout, e a configuração centróide comum foi a que apresentou o melhor casamento.

Neste trabalho, a recomendação de se empregar apenas capacitores unitários idênticos é satisfeita com a aproximação das razões de capacitâncias por números racionais. Assim, uma vez que as razões de capacitâncias do filtro tenham sido aproximadas, o próximo passo é a elaboração do *layout* das matrizes de capacitores unitários. Entretanto, quando o número de capacitores unitários é grande, encontrar o arranjo em centróide comum é uma tarefa bastante difícil e que consome muito tempo do engenheiro de *layout*.

As primeiras ferramentas desenvolvidas para a automação do projeto de *layout* de circuitos integrados não apresentavam uma preocupação com a necessidade de se arranjar os capacitores unitários com geometria de centróide comum [24, 25]. A principal preocupação desses trabalhos era produzir *layouts* compactos e com simples roteamento. O posicionamento dos capacitores unitários empregando-se geometrias simétricas e com centróide comum passou a ser considerado, posteriormente, em diversos outros trabalhos [26–41].

Em [28] e [33] são apresentados métodos automáticos para o posicionamento de capacitores unitários em uma matriz com simetria de centróide comum. Entretanto, o método apresentado nesses trabalhos também lida com matrizes, nas quais alguns capacitores não apresentam as mesmas dimensões que os unitários. Essa característica aumenta consideravelmente a complexidade do algoritmo de posicionamento, porque, além de se obter um *layout* em centróide comum, também busca-se encaixar os capacitores não unitários na matriz de forma que o layout seja o mais compacto possível.

Outros trabalhos consideram o caso mais geral de se posicionar, em centróide comum, blocos analógicos genéricos com dimensões diferentes [32,34,37,40,41]. Como não há uma uniformidade nas dimensões físicas, além de satisfazer a restrição de centróide comum, os métodos de posicionamento também têm que buscar a solução que produz o layout mais compacto, ou seja, o que minimiza os espaços vazios entre os blocos. Para isso, foram desenvolvidas diferentes estruturas de dados para representar o arranjo geométrico dos blocos no layout, onde o objetivo é acelerar a busca pela solução ótima.

No presente trabalho, as matrizes de capacitores contêm apenas capacitores unitários idênticos. Dessa forma, qualquer que seja o arranjo dos capacitores na matriz, o *layout* produzido será compacto, pois todos os capacitores unitários se encaixam uniformemente, sem o risco de deixar grandes espaços vazios entre eles. Essa característica simplifica a estrutura de dados utilizada na representação do *layout* e acelera a busca pela solução ótima.

Apesar de ser eficaz na compensação de gradientes de temperatura e variações de processo em capacitores MOS, a geometria com centróide comum tem sua aplicação limitada aos casos em que o número de capacitores unitários que integram cada um dos capacitores do filtro é par, ou quando existe, no máximo, um único capacitor do filtro com um número ímpar de unitários associados [36]. Assim sendo, nem sempre será possível encontrar um arranjo em centróide comum para as razões de capacitâncias aproximadas por quaisquer razões de inteiros.

Nos trabalhos citados acima, sempre que não é possível posicionar os componentes em centróide comum, os métodos desenvolvidos buscam o arranjo que seja o mais próximo possível do ideal. Em [36], é apresentado um método para o layout de

transistores que devem estar muito bem casados. Nesse método, os transistores são quebrados automaticamente em um número par de transistores menores em paralelo, com o objetivo de se obter perfeitamente a configuração com centróide comum. No presente trabalho, o número de capacitores unitários associados a cada capacitor do filtro é determinado pelo método de aproximação descrito no Capítulo II, e não necessariamente corresponde a um número inteiro adequado para o arranjo em centróide comum. Uma forma de contornar essa limitação seria incluir uma restrição no problema de aproximação das razões de capacitâncias que tornasse viáveis apenas soluções onde as razões aproximadas apresentassem numeradores e denominadores pares. Entretanto, essa restrição adicional fatalmente levaria a soluções com numeradores e denominadores maiores, o que aumentaria a área ocupada pelo filtro e o seu consumo de energia.

Por outro lado, em [26] é apresentado um modelo algébrico visando encontrar um arranjo de componentes em um *layout*, de forma que o circuito implementado seja insensível a gradientes de variação de parâmetros. O trabalho citado demonstra que o arranjo em centróide comum é uma das possíveis soluções para o problema, mas não é a única. Entretanto, não é mostrado nenhum método para encontrar as outras soluções que, mesmo não estando arranjadas em centróide comum, tornam o circuito insensível a gradientes de variação de parâmetros.

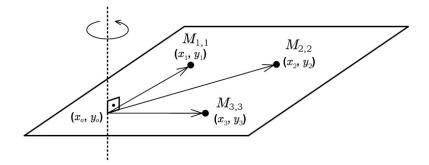

No presente trabalho, será apresentado um método, baseado em simulated annealing [42], que consegue encontrar, quando for possível, arranjos dos capacitores unitários, sem centróide comum, que tornam as razões de capacitâncias insensíveis a gradientes de variação de parâmetros. Com esse método, será possível encontrar layouts ótimos, mesmo quando a configuração centróide comum não for possível. Além disso, será mostrado que pode haver mais de um arranjo ótimo para uma mesma matriz de capacitores unitários. Dessa forma, pode-se também otimizar o layout com respeito a outros efeitos — como, por exemplo, a atenuação de erros aleatórios ou a simplificação do roteamento — e fazer com que a condição de insensibilidade do arranjo seja apenas uma restrição do problema.

No Capítulo III, é apresentado o método para a otimização do layout das matrizes de capacitores unitários desenvolvido neste trabalho. O método será aplicado a alguns exemplos ilustrativos a fim de se verificar o seu desempenho. Além disso, o método será empregado na obtenção do *layout* das matrizes de capacitores unitários dos filtros a capacitores chaveados projetados no Capítulo II.

### I.3 - FILTRO CONTÍNUO NO TEMPO

Mesmo sendo analógicos, os filtros a capacitores chaveados são sistemas discretos no tempo. A principal característica que os difere dos filtros digitais é o fato de que

as amostras de sinal processadas pelos filtros a capacitores chaveados podem assumir qualquer valor dentro do intervalo de sua faixa dinâmica. Os sinais processados pelos filtros digitais, por outro lado, só podem assumir valores discretos determinados pelo número de bits adotados na representação das amostras. Portanto, filtros a capacitores chaveados são contínuos em amplitude, enquanto que os digitais são discretos em amplitude.

No entanto, apesar das diferenças, ambos lidam com sinais amostrados. Por essa razão, filtros a capacitores chaveados também necessitam que o sinal de entrada tenha seu espectro de freqüências limitado por um filtro passa-baixa, a fim de se evitar o fenômeno de aliasing [43,44]. Esse filtro passa-baixa, também conhecido como filtro anti-aliasing, deve ser contínuo no tempo, pois, caso contrário, este também iria precisar de um filtro anti-aliasing.

Diferentemente dos filtros chaveados, os coeficientes da função de transferência de filtros contínuos no tempo não dependem dos valores relativos de componentes — como as razões de capacitâncias nos filtros a capacitores chaveados. Conseqüentemente, filtros contínuos no tempo são bastante sensíveis às variações dos parâmetros do processo de fabricação. Por essa razão, necessitam de esquemas de sintonia automática para ajustar alguns componentes do filtro a fim de compensar todas as variações [3]. As técnicas mais amplamente conhecidas para a implementação de filtros contínuos no tempo em circuitos integrados CMOS são os filtros MOSFET-C e os OTA-C.

Os filtros MOSFET-C são obtidos a partir de filtros RC-ativos, onde os resistores são substituídos por MOSFET's (Metal Oxide Semiconductor Field Effect Transistors) operando na região de triodo [3]. Uma das vantagens dessa substituição é o fato de transistores ocuparem bem menos área em um circuito integrado do que resistores. Mas a principal razão para substituir os resistores por MOSFET's é a necessidade de se controlar a resistência equivalente desses transistores para sintonizar o filtro, compensando as variações que afetam os capacitores. A principal desvantagem dessa técnica é o fato de que transistores MOS operando na região de triodo não são lineares como resistores, levando a distorções nos sinais processados pelo filtro [2]. A estratégia mais empregada para atenuar os efeitos desse comportamento não linear é o emprego de topologias diferenciais para eliminar os harmônicos de ordem par [2]. Outra grande desvantagem dessa técnica é a necessidade de amplificadores operacionais com baixa impedância de saída, o que é difícil de se obter com circuitos CMOS.

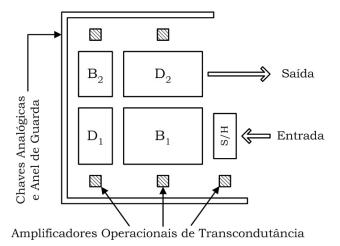

Devido às desvantagens mencionadas acima, a técnica mais amplamente adotada na implementação de filtros analógicos é a OTA-C, que emprega circuitos com OTA's (Operational Transconductance Amplifiers) e capacitores. Amplificadores operacionais de transcondutância são bem mais simples de se implementar em tecnologias

CMOS, justamente porque esses componentes necessitam de impedâncias de saída elevadas. Além disso, a sintonia destes filtros é realizada variando-se a transcondutância dos OTA's, e existem na literatura diversas técnicas bastante eficientes para o ajuste da transcondutância de um OTA [2, 45, 46]. Conseqüentemente, o filtro anti-aliasing desenvolvido neste trabalho será implementado usando a técnica OTA-C.

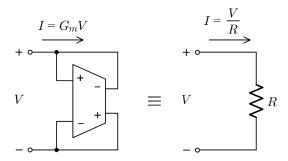

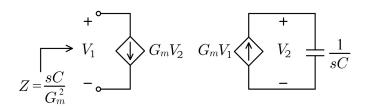

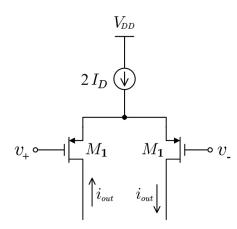

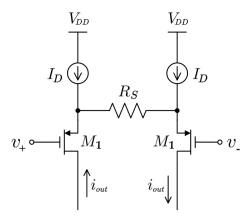

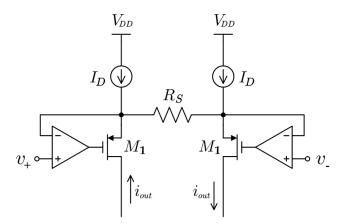

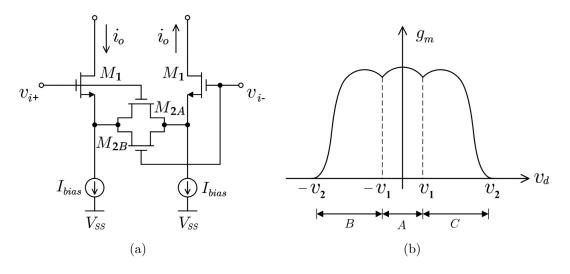

No projeto de filtros OTA-C, uma das questões mais críticas é a linearidade da relação entre a corrente na saída do OTA e a sua tensão diferencial de entrada. Um par diferencial simples, por exemplo, não apresenta um comportamento linear. Entretanto, esse comportamento não linear não representa um problema crítico em amplificadores operacionais em malha fechada, pois a tensão diferencial de entrada é usualmente muito baixa — idealmente nula. Por outro lado, em filtros OTA-C, os amplificadores operacionais de transcondutância operam com tensões diferenciais de entrada bastante significativas, e o comportamento não linear do par diferencial degradaria a faixa dinâmica do filtro. Por essa razão, diversas estratégias foram desenvolvidas para melhorar a linearidade de um par diferencial [47–81], permitindo que filtros OTA-C pudessem ser implementados com uma ampla faixa dinâmica. Uma visão geral das principais estratégias é apresentada no Capítulo IV.

Um outro problema relacionado ao projeto de filtros contínuos no tempo é que, ao contrário do que acontece em filtros chaveados, pólos em baixas freqüências não são facilmente realizáveis. Considere, por exemplo, um filtro de primeira ordem com um pólo em 10 kHz. Um filtro RC-ativo com esse pólo necessitaria ter  $1/RC = 2\pi \cdot 10^4$ . Se considerarmos um capacitor C na ordem de 1 pF — um valor razoável para ser construído em um circuito integrado —, o valor do resistor R deverá ser de aproximadamente 16 M $\Omega$ , o que é proibitivamente grande para ser integrado. No caso de filtros OTA-C, os pólos seriam dados em função de  $G_m/C$ , onde  $G_m$  representa a transcondutância do OTA. Nesse caso, para um capacitor C de 1 pF, a transcondutância  $G_m$  deverá ser de 62,5 nA/V, aproximadamente. Porém, a construção de um OTA com esse valor de transcondutância não é uma tarefa trivial, pois necessitaria de um par diferencial com transistores exageradamente longos. Para contornar esse problema, foram desenvolvidas técnicas de projeto de transcondutores para aplicações de baixas freqüências [82–97]. As principais são discutidas no Capítulo IV.

No presente trabalho, uma topologia de OTA é proposta para atingir transcondutâncias na faixa de nA/V, com comportamento linear em uma ampla faixa da tensão diferencial de entrada. Esse OTA será empregado na construção de um filtro anti-aliasing para o filtro passa-faixa a capacitores chaveados projetado no Capítulo II. O projeto do filtro anti-aliasing, assim como a topologia proposta para o OTA e os resultados obtidos através de simulação são apresentados no Capítulo IV.

## CAPÍTULO II

# Aproximação das Razões de Capacitâncias

De acordo com o Capítulo I, a principal motivação para aproximar as razões de capacitâncias de um filtro a capacitores chaveados por números racionais é a possibilidade de se implementar cada capacitor do filtro como uma associação em paralelo de capacitores unitários idênticos. Assim, usando técnicas de layout adequadas, é possível obter um excelente casamento entre tais capacitores e, conseqüentemente, aumentar a robustez do filtro com relação a variações dos parâmetros do processo de fabricação CMOS. Entretanto, conforme mencionado, a desvantagem de realizar tais aproximações é a produção de erros na resposta em freqüência do filtro. Além disso, foi mostrado que o erro de aproximação de uma razão pode ser feito arbitrariamente pequeno quanto se queira, com a desvantagem de que quanto menor o erro, maiores serão os numeradores e os denominadores inteiros das aproximações racionais, levando a um compromisso entre precisão e a área ocupada pelo circuito.

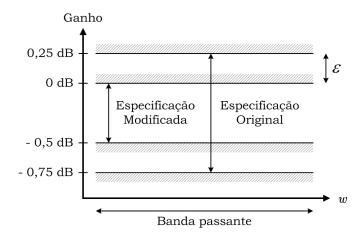

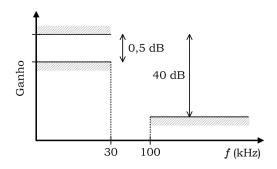

Para contornar o problema do compromisso entre precisão e área, propõe-se, inicialmente, projetar o filtro a capacitores chaveados com especificações mais exigentes que as originais — reduzindo a máxima atenuação tolerada na banda passante, por exemplo. Uma vez obtida a função de transferência ideal para as especificações modificadas, o problema passa a ser o de aproximar cada uma das razões de capacitâncias por números racionais com os menores numeradores e denominadores inteiros possíveis, de forma que o filtro aproximado satisfaça às especificações originais, mesmo com os erros causados pelas aproximações.

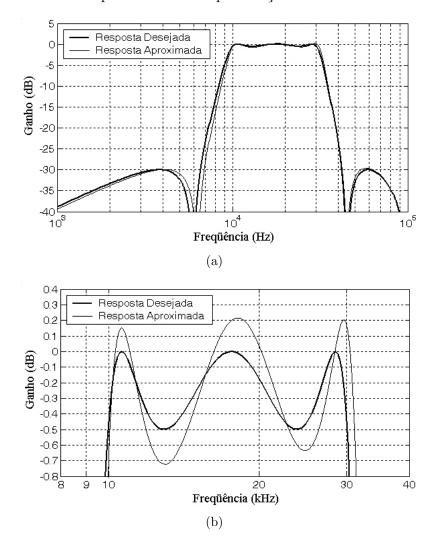

No presente capítulo, é proposta uma metodologia para encontrar uma solução para o problema descrito acima. Tal metodologia é aplicada a dois projetos de filtros a capacitores chaveados que empregam topologias freqüentemente utilizadas na indústria. O primeiro é um filtro passa-banda obtido por simulação de uma rede *lad*-

der passiva, enquanto que o segundo emprega uma cascata de seções biquadráticas (biquads) para implementar um filtro passa-baixa. Na Seção II.1, são apresentados os projetos preliminares de ambos os filtros. Na Seção II.2, é apresentado o método de aproximação das razões de capacitâncias. Os resultados obtidos com a aplicação do método aos dois casos exemplo são apresentados na Seção II.3.

### II.1 - FILTROS A CAPACITORES CHAVEADOS

Nesta seção, é apresentada uma breve descrição de ambos os filtros a capacitores chaveados empregados como exemplos. Tais filtros empregam técnicas bem conhecidas na literatura para a obtenção dos valores dos coeficientes da função de transferência e, conseqüentemente, das razões de capacitâncias que serão aproximadas posteriormente. Em cada projeto, as especificações originais foram alteradas através da redução da máxima atenuação permitida na banda passante, com o objetivo de compensar os erros oriundos das aproximações.

### II.1.1 - SIMULAÇÃO DE REDE LADDER

As especificações do projeto preliminar do filtro a capacitores chaveados são:

- Banda passante entre 10 e 30 kHz;

- Banda de rejeição abaixo de 5 kHz e acima de 50 kHz;

- Máxima atenuação na banda passante de 1,0 dB;

- Mínima atenuação na banda de rejeição de 30 dB.

A especificação original da máxima atenuação na banda passante será reduzida de 1 dB para 0,5 dB, a fim de levar em consideração o efeito dos erros de aproximação das razões. É importante mencionar que quanto maior for a redução da máxima atenuação na banda passante em relação às especificações originais, mais relaxadas serão as tolerâncias para a aproximação das razões de capacitâncias. Conseqüentemente, menores serão os números inteiros nos numeradores e denominadores das razões aproximadas. Por outro lado, uma redução excessiva da máxima atenuação da banda passante pode fazer com que seja necessário empregar um filtro com ordem maior que aquela necessária para satisfazer às especificações originais. Assim, não faz sentido tentar economizar área de silício através da redução do número de capacitores unitários, se isso implicar em um aumento da ordem do filtro. Portanto, a alteração nas especificações originais deve ser realizada com cautela por parte do projetista.

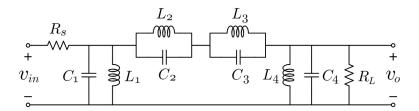

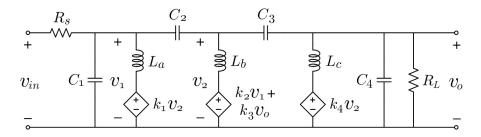

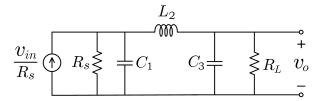

Para satisfazer às novas especificações, foi adotada uma aproximação elíptica de sexta ordem. Usando métodos clássicos de síntese de redes passivas [98], obtém-se o protótipo em rede *ladder* duplamente terminada apresentado na Fig. II.1.

Figura II.1: Rede *ladder* duplamente terminada, empregada como protótipo do filtro a capacitores chaveados.

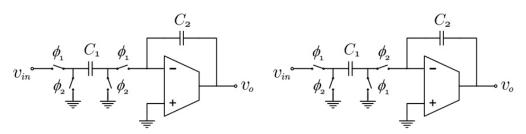

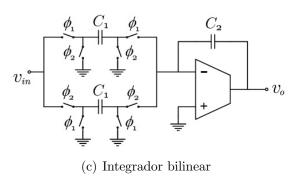

Com o protótipo passivo pronto, o próximo passo consiste em escrever as equações de estado da rede ladder, e implementar cada uma delas empregando integradores a capacitores chaveados — como os da Fig. II.2 [1]. Entretanto, no protótipo passivo da Fig. II.1, os indutores  $L_1$ ,  $L_2$ ,  $L_3$  e  $L_4$  formam um ciclo fechado, indicando que a rede ladder sintetizada apresenta uma freqüência natural igual a zero. Isso implicará em problemas de estabilidade do filtro a capacitores chaveados, em virtude das tensões de offset dos amplificadores operacionais presentes nos integradores [1].

(a) Integrador backward de Euler.

(b) Integrador forward de Euler.

Figura II.2: Integradores a capacitores chaveados.

Adotando a estratégia apresentada em [99], o ciclo de indutores pode ser substituído pelo seu equivalente de Thévenin, visto dos terminais aos quais o ciclo se conecta ao restante da rede *ladder*. Como a freqüência natural em zero está relacionada apenas com a corrente no ciclo de indutores, sem afetar as tensões em seus

Figura II.3: Equivalente Thévenin do ciclo de indutores presente na rede ladder original.

terminais, o equivalente de Thévenin não apresentará o mesmo problema da frequência natural em zero. Na Fig. II.3, é apresentado o circuito equivalente de Thévenin do ciclo de indutores, onde:

$$L_a = \frac{L_1 L_2}{L_1 + L_2};$$

$k_1 = \frac{L_1}{L_1 + L_2};$  (II.1)

$$L_b = \frac{L_2 L_3}{L_2 + L_3}, \qquad k_2 = \frac{L_3}{L_2 + L_3}, \qquad k_3 = \frac{L_2}{L_2 + L_3};$$

(II.2)

$$L_c = \frac{L_3 L_4}{L_3 + L_4}, \qquad k_4 = \frac{L_4}{L_3 + L_4}.$$

(II.3)

Substituindo o circuito equivalente de Thévenin da Fig. II.3 na rede *ladder* da Fig. II.1, obtemos o circuito da Fig. II.4.

Figura II.4: Rede *ladder* com o ciclo de indutores substituído pelo seu equivalente de Thévenin.

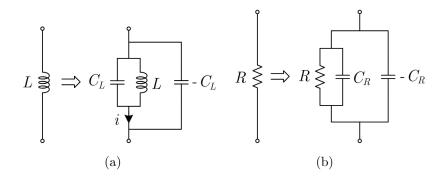

Para a implementação das equações de estado do protótipo, devemos substituir cada uma das operações de integração contínuas no tempo, por integrações discretas. Entre as integrações discretas no tempo, temos a bilinear (trapezoidal), a forward e a backward de Euler [1]. Entre essas, a mais eficiente é a bilinear, a qual será empregada neste projeto. Entretanto, os integradores de Euler a capacitores chaveados são significativamente mais simples e ocupam menos área que o circuito do integrador bilinear — vide Fig. II.2. Por essa razão, em [99], é apresentado um conjunto de modificações — apresentadas na Fig. II.5 — que podem ser aplicadas a uma rede ladder, de forma que, ao se aplicar a integração bilinear às suas equações de estado,

Figura II.5: Transformações a serem aplicadas aos indutores (a) e aos resistores (b) da rede ladder.

estas podem ser simplificadas algebricamente até que cada integração seja expressa em termos de um dos integradores de Euler. Desse modo, mesmo substituindo as integrais contínuas no tempo por integrações bilineares, o filtro a capacitores chaveados poderá ser implementado empregando uma combinação de integradores de Euler.

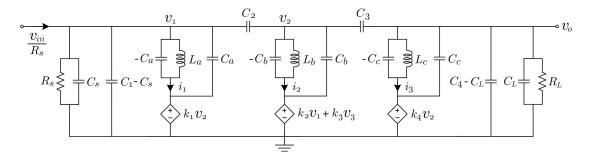

Aplicando as modificações mostradas na Fig. II.5 à rede *ladder* da Fig. II.4, obtém-se o circuito apresentado na Fig. II.6.

Figura II.6: Rede ladder modificada.

Primeiramente, adiciona-se, em paralelo com cada um dos indutores, um capacitor negativo hipotético, conforme mostrado na Fig. II.5(a). A fim de que a função de transferência do filtro não seja alterada, um capacitor positivo, com o mesmo módulo de capacitância, deve ser adicionado em paralelo para anular o efeito do primeiro. De acordo com [99], os capacitores  $C_a$ ,  $C_b$  e  $C_c$  na Fig. II.6 são dados por:

$$C_a = \frac{T^2}{4L_a}, \qquad C_b = \frac{T^2}{4L_b}, \qquad C_c = \frac{T^2}{4L_c};$$

(II.4)

onde T é o período de amostragem do filtro a capacitores chaveados — neste projeto,  $T=5~\mu s$ . Para que essas modificações tenham o efeito desejado sobre as equações de estado da rede ladder, é necessário tomar como variáveis de estado as correntes dos ramos com os indutores e seus respectivos capacitores negativos em paralelo, ao invés de tomar apenas as correntes nos indutores, como normalmente é feito. Assim,

as correntes  $i_1$ ,  $i_2$  e  $i_3$ , apresentadas na Fig. II.6, serão escolhidas como variáveis de estado.

Com os resistores da rede, o procedimento adotado é bastante semelhante. Primeiramente, o ramo formado pela tensão de entrada em série com o resistor  $R_S$ , mostrado na Fig. II.4, é substituído pelo seu circuito equivalente de Norton. Posteriormente, é adicionado um capacitor em paralelo com cada resistor, conforme mostrado na Fig. II.5(b). Para compensar o efeito desses elementos adicionais, também são incluídos, em paralelo, capacitores negativos com o mesmo módulo dos anteriores. Os capacitores negativos são, então, absorvidos pelos capacitores  $C_1$  e  $C_4$  já existentes na rede, conforme mostrado na Fig. II.6. Os capacitores adicionais  $C_S$  e  $C_L$  são dados por:

$$C_s = \frac{T}{2R_s}, \qquad C_L = \frac{T}{2R_L}. \tag{II.5}$$

Para completar o conjunto de variáveis de estado do circuito da Fig. II.6, devemos escolher as tensões dos nós, indicadas por  $v_1$ ,  $v_2$  e  $v_o$ .

A equação de estado de  $v_1$  pode ser obtida por meio da equação da Lei das Correntes de Kirchhoff aplicada ao nó do circuito referente a essa tensão. Usando Transformada de Laplace<sup>1</sup>, obtém-se:

$$V_{1} = \frac{1}{(C_{1} - C_{s} + C_{a} + C_{2})} \cdot \frac{1}{s} \cdot \left[ \frac{V_{in}}{R_{s}} - \left( \frac{1}{R_{s}} + sC_{s} \right) V_{1} - I_{1} + s \left( C_{2} + k_{1}C_{a} \right) V_{2} \right].$$

(II.6)

Substituindo em (II.6) a expressão de  $C_s$  dada em (II.5), obtém-se:

$$V_{1} = \frac{1}{(C_{1} - C_{s} + C_{a} + C_{2})} \cdot \frac{1}{s} \cdot \left[ \frac{V_{in}}{R_{s}} - \left( 1 + s \frac{T}{2} \right) \frac{V_{1}}{R_{s}} - - I_{1} + s \left( C_{2} + k_{1} C_{a} \right) V_{2} \right].$$

(II.7)

Substituindo a integração contínua 1/s pela bilinear

$$\frac{1}{s} \to \frac{T}{2} \cdot \frac{1+z^{-1}}{1-z^{-1}},$$

(II.8)

obtém-se a versão discreta no tempo da equação de estado de  $v_1$ :

$$V_{1} = \frac{1}{(C_{1} - C_{s} + C_{a} + C_{2})} \cdot \frac{1}{1 - z^{-1}} \cdot \left[ (1 + z^{-1}) \frac{T}{2R_{s}} V_{in} - \frac{T}{R_{s}} V_{1} - \frac{T}{2} (1 + z^{-1}) I_{1} + (1 - z^{-1}) (C_{2} + k_{1}C_{a}) V_{2} \right].$$

(II.9)

<sup>&</sup>lt;sup>1</sup>Neste texto emprega-se a convenção de usar letras maiúsculas para designar variáveis no domínio da freqüência, e letras minúsculas para designar variáveis no domínio do tempo.

Definindo-se os seguintes parâmetros:

$$\frac{A_1}{A} = \frac{T}{2R_s (C_1 - C_s + C_a + C_2)}, \quad \frac{A_2}{A} = \frac{T}{R_s (C_1 - C_s + C_a + C_2)},

\frac{A_3}{A} = \frac{T}{2(C_1 - C_s + C_a + C_2)}, \quad \frac{A_4}{A} = \frac{(C_2 + k_1 C_a)}{(C_1 - C_s + C_a + C_2)}.$$

(II.10)

Pode-se reescrever a equação (II.9) de uma forma mais simplificada:

$$V_{1} = \frac{1}{A} \cdot \frac{1}{1 - z^{-1}} \cdot \left[ A_{1} \left( 1 + z^{-1} \right) V_{in} - A_{2} V_{1} - A_{3} \left( 1 + z^{-1} \right) I_{1} + A_{4} \left( 1 - z^{-1} \right) V_{2} \right].$$

(II.11)

Para obter a equação de estado da variável  $i_1$ , basta aplicar a Lei das Tensões de Kirchhoff ao ramo paralelo  $L_a(-C_a)$  do circuito da Figura II.6. Assim, obtém-se:

$$\left(\frac{sL_a}{1 - C_a L_a s^2}\right) I_1 = V_1 - k_1 V_2.$$

(II.12)

Substituindo o termo  $C_a$  pela sua expressão apresentada em (II.4), na equação (II.12), obtém-se:

$$\left(\frac{s}{1 - \frac{T^2}{4}s^2}\right) L_a I_1 = V_1 - k_1 V_2.$$

(II.13)

Assim, aplicando a transformação bilinear à equação (II.13), obtém-se a versão discreta no tempo da equação de estado:

$$(1+z^{-1})I_1 = \frac{z^{-1}}{1-z^{-1}} \cdot \left[\frac{2T}{L_a}V_1 - \frac{2Tk_1}{L_a}V_2\right].$$

(II.14)

Analogamente ao caso da equação de estado da variável  $v_1$ , definem-se os seguintes parâmetros:

$$\frac{B_1}{B} = \frac{2T}{L_a}, \quad \frac{B_2}{B} = \frac{2Tk_1}{L_a}.$$

(II.15)

Assim, pode-se reescrever a equação (II.14) de maneira mais simplificada:

$$(1+z^{-1})I_1 = \frac{1}{B} \cdot \frac{z^{-1}}{1-z^{-1}} \cdot [B_1V_1 - B_2V_2].$$

(II.16)

Para a equação de estado da variável  $v_2$ , aplica-se a Lei das Correntes de Kirchhoff ao nó do circuito referente a esta tensão, obtendo-se:

$$V_2 = \frac{1}{C_b + C_2 + C_3} \cdot \frac{1}{s} \cdot \left[ s \left( C_2 + k_2 C_b \right) V_1 + s \left( C_3 + k_3 C_b \right) V_o - I_2 \right]. \tag{II.17}$$

Aplicando-se diretamente a transformação bilinear à equação (II.17), obtém-se a versão discreta no tempo da equação de estado de  $v_2$ :

$$V_{2} = \frac{1}{C_{b} + C_{2} + C_{3}} \cdot \frac{1}{1 - z^{-1}} \cdot \left[ \left( 1 - z^{-1} \right) \left( C_{2} + k_{2}C_{b} \right) V_{1} + \left( 1 - z^{-1} \right) \left( C_{3} + k_{3}C_{b} \right) V_{o} - \frac{T}{2} \left( 1 + z^{-1} \right) I_{2} \right].$$

(II.18)

Analogamente aos casos anteriores, definem-se os seguintes parâmetros:

$$\frac{D_1}{D} = \frac{C_2 + k_2 C_b}{C_b + C_2 + C_3}, \qquad \frac{D_2}{D} = \frac{C_3 + k_3 C_b}{C_b + C_2 + C_3},

\frac{D_3}{D} = \frac{T}{2(C_b + C_2 + C_3)}.$$

(II.19)

Assim, a equação de estado de  $v_2$  pode ser expressa por:

$$V_2 = \frac{1}{D} \cdot \frac{1}{1 - z^{-1}} \cdot \left[ D_1 \left( 1 - z^{-1} \right) V_1 + D_2 \left( 1 - z^{-1} \right) V_o - D_3 \left( 1 + z^{-1} \right) I_2 \right]. \quad (II.20)$$

Assim como no caso da corrente  $i_1$ , a equação de estado da variável  $i_2$  pode ser obtida a partir da aplicação da Lei das Tensões de Kirchhoff ao ramo paralelo  $L_b(-C_b)$  do circuito da Figura II.6:

$$\left(\frac{sL_b}{1 - C_b L_b s^2}\right) I_2 = V_2 - k_2 V_1 - k_3 V_o.$$

(II.21)

Substituindo o termo  $C_b$  em (II.21) pela expressão dada em (II.4), obtém-se:

$$\left(\frac{s}{1 - \frac{T^2}{4}s^2}\right) L_b I_2 = V_2 - k_2 V_1 - k_3 V_o.$$

(II.22)

Assim, aplicando-se a transformação bilinear à equação (II.22), obtém-se a versão discreta no tempo da equação de estado de  $i_2$ :

$$(1+z^{-1})I_2 = \frac{z^{-1}}{1-z^{-1}} \cdot \left[ \frac{2T}{L_b} V_2 - \frac{2Tk_2}{L_b} V_1 - \frac{2Tk_3}{L_b} V_o \right].$$

(II.23)

Agora, definem-se os seguintes parâmetros:

$$\frac{E_1}{E} = \frac{2T}{L_b}, \qquad \frac{E_2}{E} = \frac{2Tk_2}{L_b},

\frac{E_3}{E} = \frac{2Tk_3}{L_b}.$$

(II.24)

Assim, a equação de estado (II.23) pode ser reescrita da seguinte forma:

$$(1+z^{-1})I_2 = \frac{1}{E} \cdot \frac{z^{-1}}{1-z^{-1}} \cdot [E_1V_2 - E_2V_1 - E_3V_o].$$

(II.25)

Para obter a equação de estado da variável  $v_o$ , aplica-se a Lei das Correntes de Kirchhoff ao nó referente a esta tensão, obtendo-se:

$$V_o = \frac{1}{C_4 - C_L + C_3 + C_c} \cdot \frac{1}{s} \cdot \left[ s \left( C_3 + k_4 C_c \right) V_2 - I_3 - \left( s C_L + \frac{1}{R_L} \right) V_o \right]. \quad (II.26)$$

Substituindo o parâmetro  $C_L$ , na equação (II.26), pela sua expressão apresentada em (II.5), obtém-se:

$$V_o = \frac{1}{C_4 - C_L + C_3 + C_c} \cdot \frac{1}{s} \cdot \left[ s \left( C_3 + k_4 C_c \right) V_2 - I_3 - \left( 1 + \frac{T}{2} s \right) \frac{V_o}{R_L} \right]. \quad \text{(II.27)}$$

Assim, aplicando-se a transformação bilinear à equação (II.27), obtém-se a versão discreta no tempo da equação de estado da variável  $v_o$ :

$$V_{o} = \frac{1}{C_{4} - C_{L} + C_{3} + C_{c}} \cdot \frac{1}{1 - z^{-1}} \cdot \left[ (C_{3} + k_{4}C_{c}) (1 - z^{-1}) V_{2} - \frac{T}{2} (1 + z^{-1}) I_{3} - \frac{T}{R_{L}} V_{o} \right].$$

(II.28)

Então, definem-se os seguintes parâmetros:

$$\frac{F_1}{F} = \frac{T}{R_L (C_4 - C_L + C_3 + C_c)}, \quad \frac{F_2}{F} = \frac{T}{2 (C_4 - C_L + C_3 + C_c)},

\frac{F_3}{F} = \frac{C_3 + k_4 C_c}{C_4 - C_L + C_3 + C_c}.$$

(II.29)

Assim, a equação de estado (II.28) pode ser reescrita da seguinte forma:

$$V_o = \frac{1}{F} \cdot \frac{1}{1 - z^{-1}} \cdot \left[ -F_1 V_o - F_2 \left( 1 + z^{-1} \right) I_3 + F_3 \left( 1 - z^{-1} \right) V_2 \right]. \tag{II.30}$$

Finalmente, a equação de estado da variável  $i_3$  pode ser obtida aplicando-se a Lei das Tensões de Kirchhoff ao ramo paralelo  $L_c(-C_c)$  do circuito da Figura II.6:

$$\left(\frac{sL_c}{1 - C_c L_c s^2}\right) I_3 = V_o - k_4 V_2.$$

(II.31)

Substituindo o parâmetro  $C_c$  pela expressão dada em (II.4), obtém-se:

$$\left(\frac{s}{1 - \frac{T^2}{4}s^2}\right) L_c I_3 = V_o - k_4 V_2.$$

(II.32)

Aplicando a transformação bilinear à equação (II.32), obtém-se a versão discreta no tempo da equação de estado de  $i_3$ :

$$(1+z^{-1})I_3 = \frac{z^{-1}}{1-z^{-1}} \cdot \left[\frac{2T}{L_c}V_o - \frac{2Tk_4}{L_c}V_2\right].$$

(II.33)

Analogamente aos casos anteriores, definem-se os seguintes parâmetros:

$$\frac{G_1}{G} = \frac{2T}{L_c}, \quad \frac{G_2}{G} = \frac{2Tk_4}{L_c}.$$

(II.34)

Assim, a equação de estado (II.33) pode ser reescrita da seguinte forma:

$$(1+z^{-1})I_3 = \frac{1}{G} \cdot \frac{z^{-1}}{1-z^{-1}} \cdot [G_1V_o - G_2V_2].$$

(II.35)

Embora a transformação bilinear tenha sido aplicada a todas as equações de estado, verifica-se que as equações (II.11), (II.20) e (II.30) empregam a integração do tipo backward de Euler, e as equações (II.16), (II.25) e (II.35) empregam a integração forward de Euler [1]. Conforme pôde ser constatado ao longo das deduções acima, essa característica das equações de estado foi alcançada devido às alterações efetuadas na rede original.

Entretanto, as equações (II.11), (II.16), (II.20), (II.25), (II.30) e (II.35) ainda não estão escritas de maneira adequada para a síntese do filtro a capacitores chaveados. Ainda há a necessidade de se reescrever essas equações, adequando-as para que possam ser implementadas com os integradores da Fig. II.2.

A função de transferência do integrador *backward* de Euler, apresentado na Figura II.2(a), é dada por:

$$\frac{V_o(z)}{V_{in}(z)} = -\frac{C_1}{C_2} \cdot \frac{1}{1 - z^{-1}}.$$

(II.36)

A função de transferência do integrador *forward* de Euler, apresentado na Figura II.2(b), é dada pela seguinte expressão:

$$\frac{V_o(z)}{V_{in}(z)} = \frac{C_1}{C_2} \cdot \frac{z^{-1}}{1 - z^{-1}}.$$

(II.37)

Por fim, a função de transferência do integrador bilinear, apresentado na Figura II.2(c), é dada por:

$$\frac{V_o(z)}{V_{in}(z)} = -\frac{C_1}{C_2} \cdot \frac{1+z^{-1}}{1-z^{-1}}.$$

(II.38)

Comparando as expressões das funções de transferência de cada um dos integradores com as equações de estado obtidas, as equações (II.11), (II.16), (II.20), (II.25),

(II.30) e (II.35) devem ser reescritos na seguinte forma:

$$(-V_1) = \frac{1}{A} \cdot \frac{-1}{1 - z^{-1}} \cdot \left[ A_1 \left( 1 + z^{-1} \right) V_{in} + A_2 (-V_1) + A_3 \left( 1 + z^{-1} \right) (-I_1) + A_4 \left( 1 - z^{-1} \right) V_2 \right];$$

(II.39)

$$(1+z^{-1})(-I_1) = \frac{1}{B} \cdot \frac{z^{-1}}{1-z^{-1}} \cdot [B_1(-V_1) + B_2V_2];$$

(II.40)

$$V_{2} = \frac{1}{D} \cdot \frac{-1}{1 - z^{-1}} \cdot \left[ D_{1} \left( 1 - z^{-1} \right) (-V_{1}) + D_{2} \left( 1 - z^{-1} \right) (-V_{o}) + D_{3} \left( 1 + z^{-1} \right) I_{2} \right];$$

(II.41)

$$(1+z^{-1})I_2 = \frac{1}{E} \cdot \frac{z^{-1}}{1-z^{-1}} \cdot [E_1V_2 + E_2(-V_1) + E_3(-V_o)];$$

(II.42)

$$(-V_o) = \frac{1}{F} \cdot \frac{-1}{1 - z^{-1}} \cdot \left[ F_1(-V_o) + F_2 \left( 1 + z^{-1} \right) (-I_3) + F_3 \left( 1 - z^{-1} \right) V_2 \right]; \quad \text{(II.43)}$$

$$(1+z^{-1})(-I_3) = \frac{1}{G} \cdot \frac{z^{-1}}{1-z^{-1}} \cdot [G_1(-V_o) + G_2V_2].$$

(II.44)

Além de expressar as equações de estado em termos das funções de transferência dos integradores de Euler, as modificações apresentadas acima foram realizadas de modo que cada variável de estado — produzida pela sua respectiva equação — fosse empregada nas demais equações a fim de produzir as as outras variáveis.

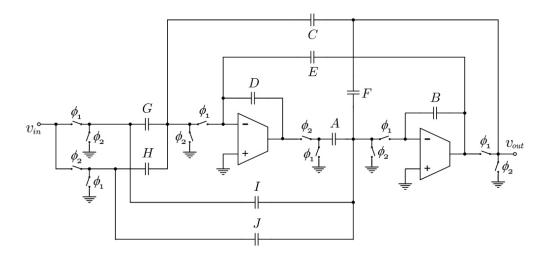

Assim, a partir das equações (II.39) até (II.44), verifica-se que as variáveis de estado produzidas por esse conjunto de equações são:  $(-V_1)$ ,  $(1+z^{-1})(-I_1)$ ,  $V_2$ ,  $(1+z^{-1})I_2$ ,  $(-V_o)$  e  $(1+z^{-1})(-I_3)$ . Além disso, todas as operações de integração utilizadas na obtenção das variáveis de estado podem ser simuladas pelos integradores de Euler apresentados na Figura II.2 — com a exceção da integração bilinear do sinal de entrada  $V_{in}$ , necessária ao cálculo da variável  $(-V_1)$ . Portanto, baseado nessas últimas equações de estado, obtemos o filtro a capacitores chaveados mostrado na Fig. II.7.

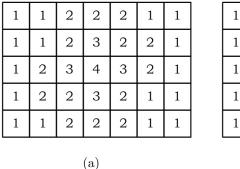

De acordo com as equações de estado, as razões de capacitâncias do filtro são obtidas através das expressões (II.10), (II.15), (II.19), (II.24), (II.29) e (II.34). Os valores numéricos dessas razões são apresentados na Tabela II.1.

Figura II.7: Filtro a capacitores chaveados obtido por simulação da rede ladder.

| RAZÃO   | Valor        | Razão   | Valor        |

|---------|--------------|---------|--------------|

| $A_1/A$ | 0,1424678518 | $E_1/E$ | 0,7325190006 |

| $A_2/A$ | 0,1988208250 | $E_2/E$ | 0,0554706315 |

| $A_3/A$ | 0,5755616856 | $E_3/E$ | 0,3649896636 |

| $A_4/A$ | 0,8591091894 | $F_1/F$ | 0,4303146309 |

| $B_1/B$ | 0,2667412564 | $F_2/F$ | 1,4774612952 |

| $B_2/B$ | 0,0519868029 | $F_3/F$ | 0,4876006943 |

| $D_1/D$ | 0,6491080042 | $G_1/G$ | 0,5014549462 |

| $D_2/D$ | 0,0874014591 | $G_2/G$ | 0,5616950041 |

| $D_3/D$ | 0,4075589886 |         |              |

| 1       | 1            | I       |              |

Tabela II.1: Valores calculados para as razões de capacitâncias.

Na Tabela II.1 são listados os valores calculados para as razões de capacitâncias que definem os coeficientes da resposta em freqüência do filtro da Fig. II.7. Os números reais listados nessa tabela deverão ser aproximados por números racionais, de modo que cada capacitor do filtro possa ser implementado através da associação em paralelo de capacitores unitários idênticos.

Entretanto, a partir da Tabela II.1, verifica-se que há grupos de razões de capacitâncias que apresentam a mesma capacitância no denominador. Essa característica é bastante freqüente em filtros a capacitores chaveados, onde os denominadores das razões são os capacitores de realimentação dos integradores [1]. Portanto, essa característica torna o problema da aproximação das razões por números racionais ainda mais complexo, pois razões com a mesma capacitância no denominador deverão ser aproximadas por números racionais com o mesmo denominador inteiro.

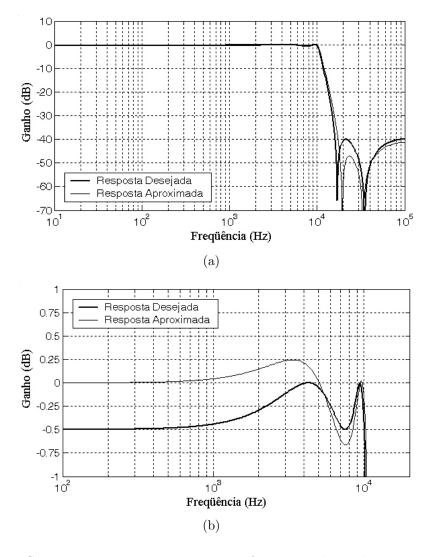

#### II.1.2 - CASCATA DE BIQUADS

O outro exemplo de projeto é um filtro a capacitores chaveados passa-baixa com as seguintes especificações:

- Banda passante até 10 kHz;

- Banda de rejeição acima de 20 kHz;

- Máxima atenuação na banda passante de 1 dB;

- Mínima atenuação na banda de rejeição de 40 dB.

Seguindo o mesmo procedimento adotado no projeto anterior, a especificação relativa à máxima atenuação permitida na banda passante foi reduzida para 0,5 dB,

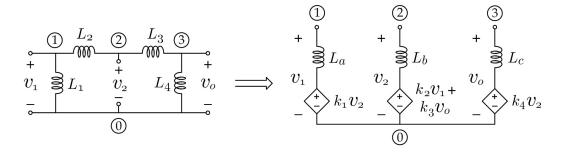

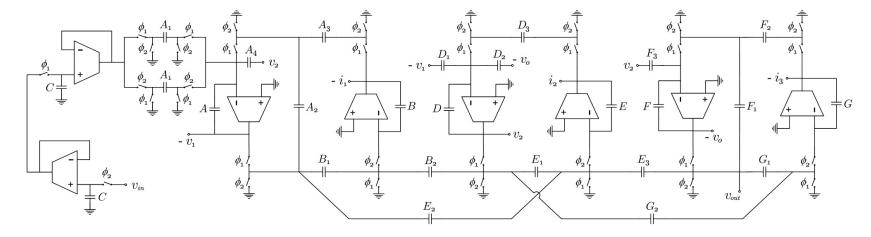

Figura II.8: O biquad de Fleischer e Laker.

com o objetivo de permitir uma margem de erro para as aproximações das razões de capacitâncias. Tais especificações são satisfeitas por um filtro elíptico de quarta ordem, onde a freqüência de amostragem escolhida foi também de 200 kHz. Dessa forma, são necessárias duas seções de *biquads* para implementar o filtro.

O circuito escolhido para as seções biquadráticas deste projeto foi o biquad de Fleischer e Laker [100], apresentado na Fig. II.8. De acordo com [100], a função de transferência desse circuito é dada por:

$$T(z) = -\frac{DI + (AG - DI - DJ) z^{-1} + (DJ - AH) z^{-2}}{(D(F + B)) + (AC + AE - DF - 2DB) z^{-1} + (DB - AE) z^{-2}}.$$

(II.45)

Com o objetivo de expressar cada um dos coeficientes da função de transferência em termos de razões de capacitâncias, dividem-se o numerador e o denominador de (II.45) pelo produto das capacitâncias dos ramos de realimentação dos integradores, ou seja, BD. Dessa forma, obtém-se a seguinte expressão:

$$T(z) = -\frac{\left(\frac{I}{B}\right) + \left(\frac{A}{B}\frac{G}{D} - \frac{I}{B} - \frac{J}{B}\right)z^{-1} + \left(\frac{J}{B} - \frac{A}{B}\frac{H}{D}\right)z^{-2}}{\left(\frac{F}{B} + 1\right) + \left(\frac{A}{B}\frac{C}{D} + \frac{A}{B}\frac{E}{D} - \frac{F}{B} - 2\right)z^{-1} + \left(1 - \frac{A}{B}\frac{E}{D}\right)z^{-2}}.$$

(II.46)

Mais uma vez, notamos que há grupos de razões de capacitâncias com o mesmo denominador, onde esses denominadores são os capacitores dos ramos de realimentação dos integradores. Os demais capacitores aparecem nos numeradores.

Os valores ideais das razões de capacitâncias de ambas as seções biquadráticas foram calculados empregando-se a metodologia de projeto descrita em [100]. Os valores calculados estão listados na Tabela II.2.

Como os valores obtidos para as capacitâncias H e F são iguais a zero, os respectivos capacitores deverão ser removidos do circuito da Fig. II.8. Além disso, como os valores calculados para I e J são iguais, os ramos contendo esses capacitores podem

| RAZÕES | Primeiro Biquad | Segundo Biquad   |

|--------|-----------------|------------------|

| A/B    | 0,1508203693    | 0,2892344370     |

| I/B    | 0,0356849731    | 0,3352717385     |

| J/B    | 0,0356849731    | 0,3352717385     |

| C/D    | 0,2579469629    | 0,3442247419     |

| E/D    | 1,6495617485    | 0,2783862246     |

| F/B    | 0,0000000000    | 0,0000000000     |

| G/D    | 0,2576069766    | $0,\!3253980015$ |

| H/D    | 0,0000000000    | 0,0000000000     |

Tabela II.2: Valores ideais das razões de capacitâncias para ambas as seções biquadráticas.

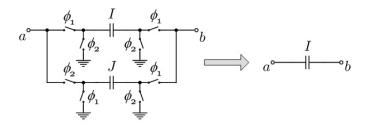

ser combinados em apenas um ramo, conforme mostrado na Fig. II.9 [100]. Com isso, serão empregados três capacitores a menos no circuito da Fig. II.8.

Figura II.9: Circuito equivalente quanto I e J são iguais.

Apesar de empregarem topologias diferentes, tanto este filtro, implementado através de uma cascata de biquads, como o anterior, obtido através da simulação das equações de estado de uma rede ladder, apresentam um conjunto similar de razões de capacitâncias, que serão aproximadas por números racionais. Em geral, o conjunto de razões de capacitâncias de um filtro a capacitores chaveados segue o mesmo padrão verificado em ambos os projetos ilustrativos apresentados aqui [1]. Portanto, o método de aproximação descrito na próxima seção poderá ser perfeitamente aplicado a outros projetos.

## II.2 - MÉTODO DE APROXIMAÇÃO

Com o objetivo de melhorar o casamento dos capacitores de um filtro a capacitores chaveados, é desejável que cada capacitor do filtro seja implementado utilizando capacitores unitários idênticos em paralelo. Para isso, é necessário aproximar cada razão de capacitâncias do filtro por números racionais, onde os números inteiros que

aparecem nos numeradores e denominadores indicam quantos capacitores unitários devem ser associados em paralelo para implementar as capacitâncias da razão.

Na Seção II.1, as especificações dos filtros foram modificadas para compensar os erros de aproximação das razões de capacitâncias. A máxima atenuação na banda passante de ambos foi alterada de 1 dB para 0,5 dB, levando a uma tolerância máxima de  $\varepsilon = 0.25$  dB na banda passante, conforme mostrado na Fig. II.10.

Figura II.10: Variação do ganho na banda passante do filtro projetado e a máxima variação tolerada devido às especificações originais.

Dessa forma, o objetivo é encontrar os números racionais, com os menores numeradores e denominadores inteiros possíveis, que aproximem as razões de capacitâncias do filtro, de modo que os erros resultantes na resposta em freqüência fiquem dentro dos limites determinados pelas especificações originais — conforme mostrado na Fig. II.10.

O problema proposto é uma otimização discreta — pois envolve encontrar numeradores e denominadores inteiros para as razões de capacitâncias — com uma restrição não linear — pois o erro na resposta em freqüência tem uma relação não linear com cada uma das razões de capacitâncias. Além disso, como a mesma razão de capacitâncias pode ser aproximada por diferentes números racionais com um erro similar, as regiões com soluções viáveis para o problema em questão — isto é, soluções que satisfazem a restrição de erro aceitável na resposta em freqüência — estão isoladas e espalhadas por todo o espaço de busca. Também deve ser lembrado que há grupos de razões de capacitâncias com a mesma capacitância no denominador, o que limita a liberdade de escolha dos números inteiros para compor os denominadores desses grupos de razões. Isso torna o problema de otimização ainda mais difícil.

Métodos clássicos de otimização são geralmente rápidos e eficientes na busca pela solução ótima de problemas contínuos, onde a função custo é bem comportada. Entretanto, eles não são aplicáveis a um problema com as características mencionadas

acima. Além disso, os métodos clássicos são muito eficientes para encontrar mínimos locais, mas não são capazes de descartar soluções locais inferiores em favor de soluções melhores na busca pelo mínimo global do problema de otimização.

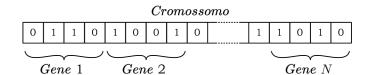

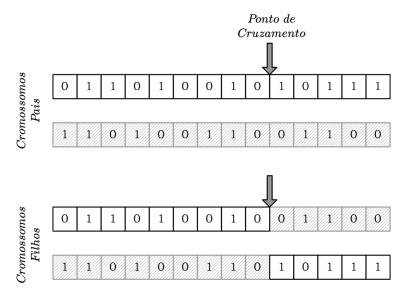

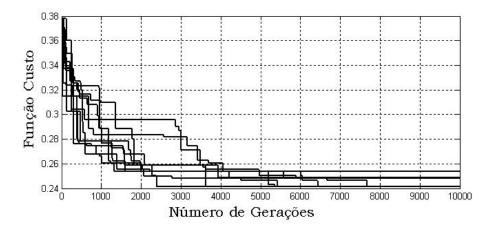

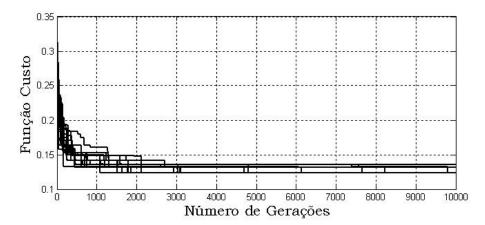

Algoritmos genéticos, por outro lado, são um conjunto de métodos estocásticos de busca baseados no processo de evolução natural das espécies vivas [20,101]. O algoritmo genético inicia com uma população de indivíduos, que são possíveis soluções para o problema de otimização — isto é, pontos no espaço de busca do problema. Os dados que caracterizam cada indivíduo são codificados em um cromossomo, que é usualmente representado por uma seqüência de bits — um vetor de bits. Além disso, a cada indivíduo é atribuída uma figura de mérito, denominada aptidão (fitness), que caracteriza o quão bom um indivíduo é em comparação com os demais da mesma população no que se refere ao objetivo do problema. A cada geração, os indivíduos mais aptos são selecionados entre os membros da população para se reproduzirem e gerarem filhos, da mesma forma que ocorre no processo de seleção natural. Então, os cromossomos dos indivíduos selecionados são recombinados para gerar sua prole. O processo de recombinação é implementado através do mecanismo de cruzamento (crossover), que consiste em trocar segmentos de cromossomo entre dois indivíduos pais, produzindo dois cromossomos filhos, que são combinações das características genéticas dos pais. A cada geração, novos indivíduos são selecionados e recombinados, produzindo a geração seguinte. O mecanismo da seleção natural permite que os melhores indivíduos sobrevivam e produzam uma prole de indivíduos que podem, potencialmente, vir a ser ainda melhores.

Com o objetivo de permitir que a população escape de mínimos locais, novas características são introduzidas na população através de mutações. Esta operação genética consiste em causar mudanças aleatórias em alguns bits que compõem os cromossomos da população.

A seleção, o cruzamento e as mutações são as operações genéticas básicas, e são repetidas a cada iteração (geração) do algoritmo. Desse modo, os indivíduos que compõem a população se tornarão soluções sucessivamente melhores a cada nova geração. Esse processo deve ser repetido até que algum critério de parada seja satisfeito. É importante deixar claro que, por ser um método de busca estocástico, não se pode garantir que a solução ótima será encontrada, mas o processo evolutivo levará a uma solução que pode ser bem próxima do ótimo [20]. Nas subseções a seguir, é apresentada uma descrição detalhada de como os operadores genéticos foram implementados neste trabalho.

### II.2.1 - Codificação dos Cromossomos

Uma das principais questões envolvendo a aplicação de algoritmos genéticos na solução de um problema de otimização é justamente como representar, na forma de

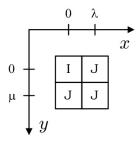

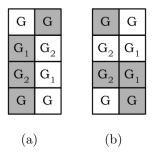

cromossomo, os dados de cada um dos pontos do espaço de busca do problema. A representação mais eficiente e mais amplamente utilizada [20] é um vetor de bits, onde cada parâmetro é codificado em um grupo de bits consecutivos no vetor. Conforme mostrado na Fig. II.11, cada seqüência de bits que corresponde a um parâmetro é denominada *gene*, em analogia à seqüência dos genes que formam os cromossomos reais dos seres vivos.

Figura II.11: Codificação dos genes em um cromossomo.

Em nosso problema, o objetivo é atribuir a cada capacitor um número inteiro, que representa o número de capacitores unitários que serão associados em paralelo para implementá-lo no circuito integrado. Para uma dada razão de capacitâncias  $C_1/C_2$ , se o denominador inteiro  $N_{C2}$  é conhecido, há apenas um único numerador inteiro  $N_{C1}$  que minimiza o erro de aproximação  $|C_1/C_2 - N_{C1}/N_{C2}|$ . Esse inteiro é dado por

$$N_{C1} = \left[ \frac{C_1}{C_2} \cdot N_{C2} \right], \tag{II.47}$$

onde os colchetes representam a operação de arredondamento pelo número inteiro mais próximo.

Conseqüentemente, se os inteiros que aproximam as capacitâncias dos denominadores de todas as razões são conhecidos, os respectivos numeradores podem ser prontamente obtidos a partir de (II.47). Dessa forma, para caracterizar um ponto no espaço de busca do problema, será necessário registrar apenas os inteiros que aparecem nos denominadores, ao invés de registrar numeradores e denominadores. Com essa simplificação, o número total de combinações possíveis para a solução do problema é reduzido enormemente, pois o número de denominadores diferentes é normalmente menor que a variedade de numeradores — conforme mostrado nos dois projetos ilustrativos da seção anterior. Essa redução na dimensão do espaço de busca contribui para acelerar a convergência do algoritmo genético.

Como os pontos do espaço de busca serão caracterizados apenas pelos valores inteiros dos denominadores, cada gene deverá conter o valor inteiro de um dos denominadores que caracterizam o indivíduo. No caso do filtro obtido por simulação de rede *ladder*, projetado na Seção II.1.1, temos seis denominadores diferentes, conseqüentemente, o cromossomo de cada indivíduo conterá seis genes. No caso do filtro implementado através da cascata de *biquads*, cada cromossomo conterá quatro genes. Em geral, como os denominadores das razões de capacitâncias são os capacitores dos

ramos de realimentação dos integradores, o número de denominadores diferentes de um filtro será igual ao número de integradores presentes no circuito, ou seja, será igual à ordem do filtro.

O próximo passo é definir quantos bits serão empregados para representar cada gene. Para isso, é necessário estimar quais são os limites inferior  $M_L$  e superior  $M_U$  dos valores inteiros que cada um dos denominadores podem assumir. Tais limites devem ser escolhidos de forma a não limitar demais o espaço de busca do problema, o que dificultaria a localização do mínimo global. Por outro lado, não é adequado definir uma faixa de valores exageradamente grande, porque isso aumentaria a quantidade de bits necessária para a representação do cromossomo, aumentando a dimensão do espaço de busca. Como a dimensão do espaço de busca é dada por  $2^N$ , onde N é o número de bits que compõem o cromossomo, a simples redução de um bit na representação do cromossomo já reduz a dimensão do espaço pela metade.

Tendo em vista que o número de capacitores unitários associados em paralelo para implementar cada capacitor do filtro tem que ser obrigatoriamente um número inteiro positivo, os limites inferiores para os denominadores são definidos como sendo os menores inteiros positivos  $M_L$  que produzem numeradores não nulos através de (II.47). De acordo com esse critério, os limites inferiores de cada um dos denominadores dos projetos exemplo foram obtidos aplicando-se (II.47) às razões de capacitâncias apresentadas nas Tabelas II.1 e II.2. Os limites obtidos estão listados na Tabela II.3. Nessa tabela,  $B_1$  e  $D_1$  são os denominadores B e D da primeira seção biquadrática do filtro biquad passa-baixa, e  $B_2$  e  $D_2$  são os denominadores da

Tabela II.3: Limites inferior e superior para os valores de cada denominador inteiro, juntamente com o número de bits necessário para representá-los.

| Filtro Ladder Passa-faixa |                 |                 |      |  |  |  |

|---------------------------|-----------------|-----------------|------|--|--|--|

| DENOMINADORES             | LIMITE INFERIOR | LIMITE SUPERIOR | Bits |  |  |  |

| A                         | 4               | 22              | 5    |  |  |  |

| B                         | 10              | 38              | 5    |  |  |  |

| D                         | 6               | 22              | 4    |  |  |  |

| E                         | 10              | 36              | 5    |  |  |  |

| F                         | 2               | 24              | 5    |  |  |  |

| G                         | 1               | 32              | 5    |  |  |  |

| Filtro Biquad Passa-baixa |                 |                 |      |  |  |  |

| DENOMINADORES             | LIMITE INFERIOR | LIMITE SUPERIOR | Bits |  |  |  |

| $B_1$                     | 28              | 53              | 5    |  |  |  |

| $D_1$                     | 4               | 27              | 5    |  |  |  |

| $B_2$                     | 3               | 24              | 5    |  |  |  |

| $D_2$                     | 4               | 44              | 6    |  |  |  |

segunda.

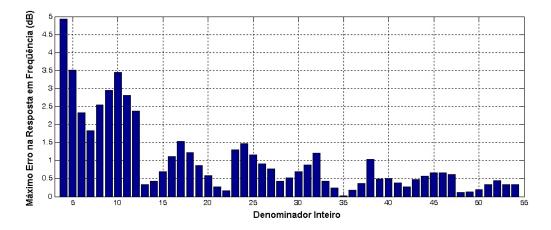

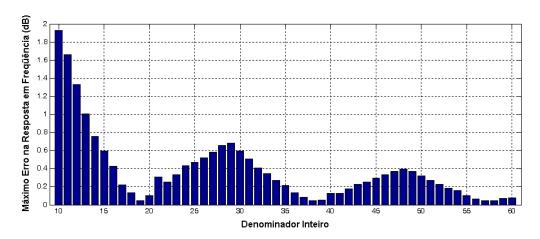

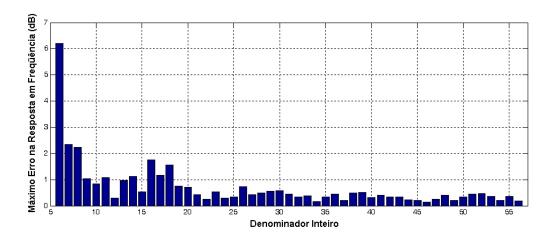

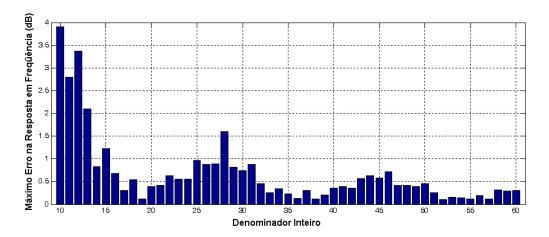

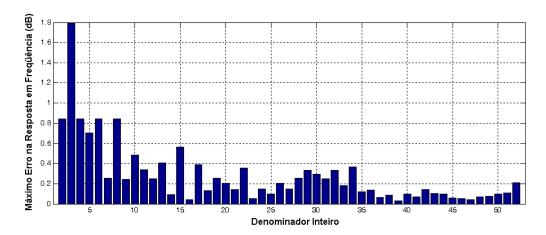

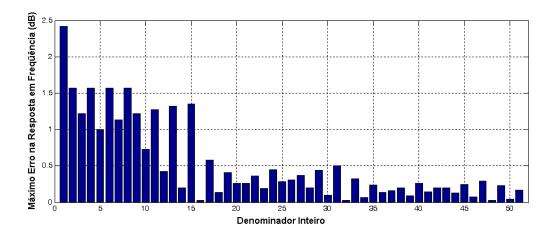

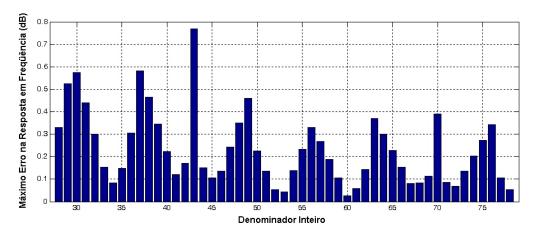

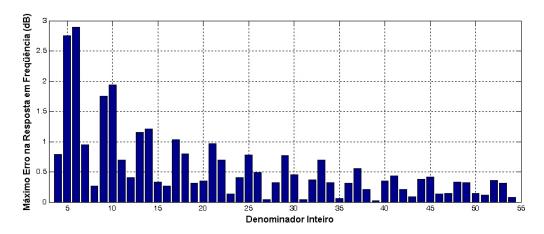

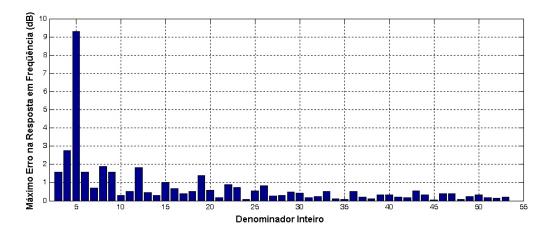

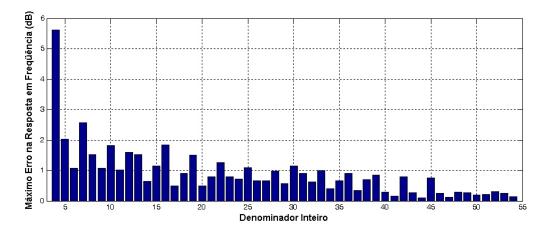

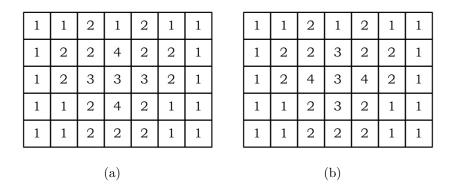

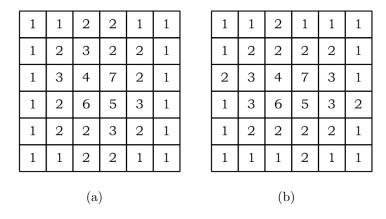

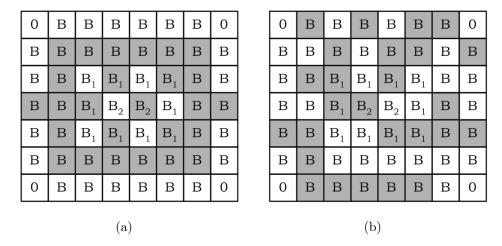

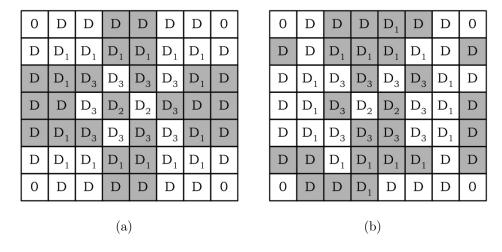

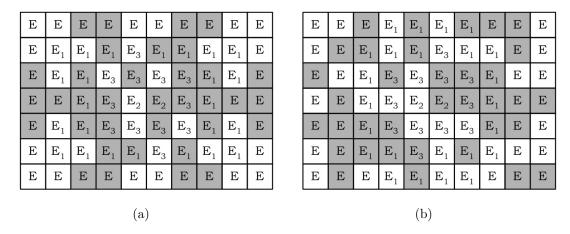

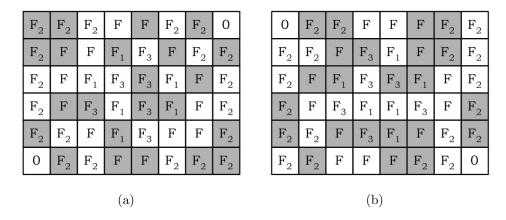

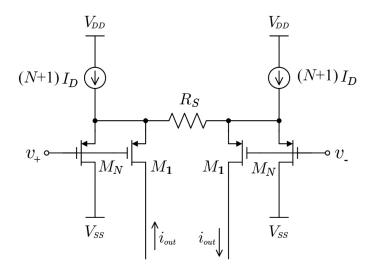

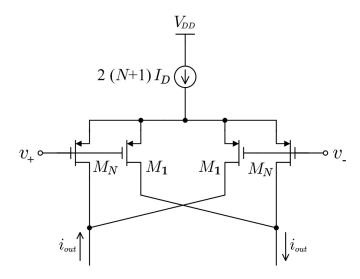

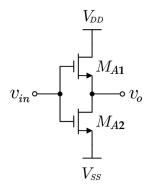

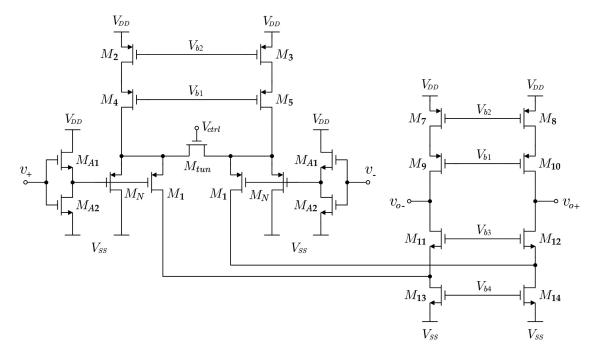

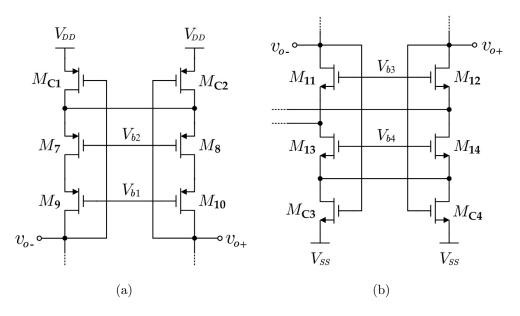

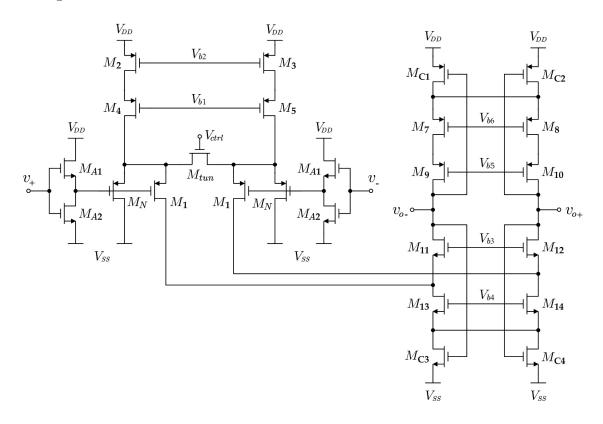

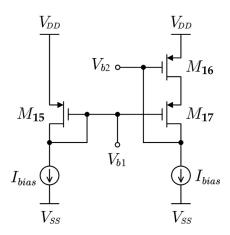

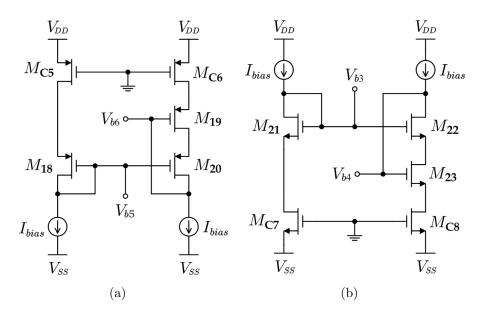

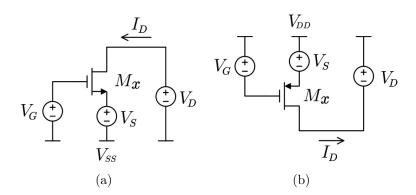

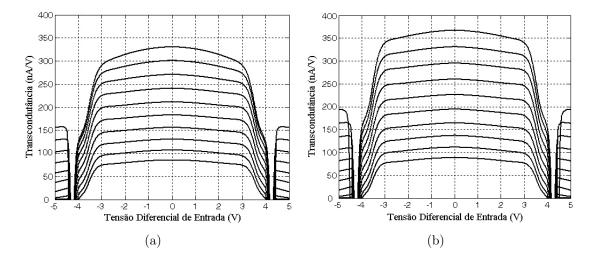

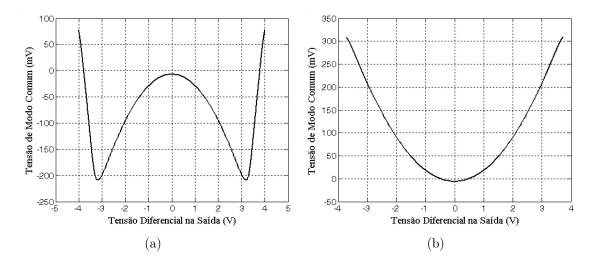

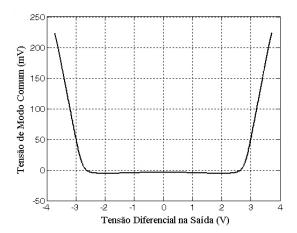

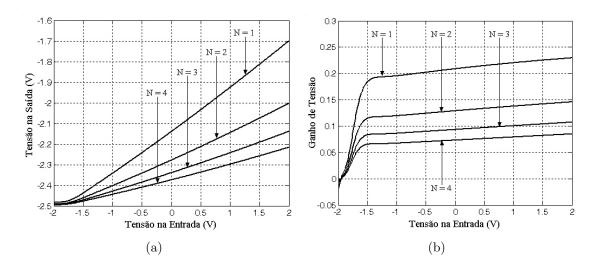

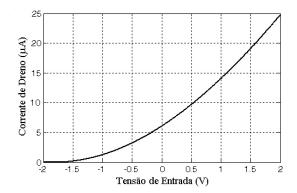

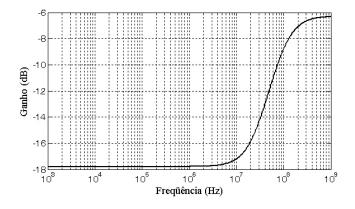

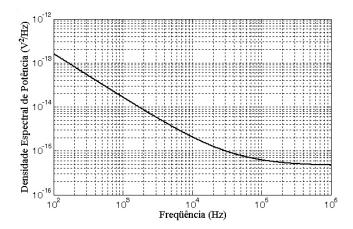

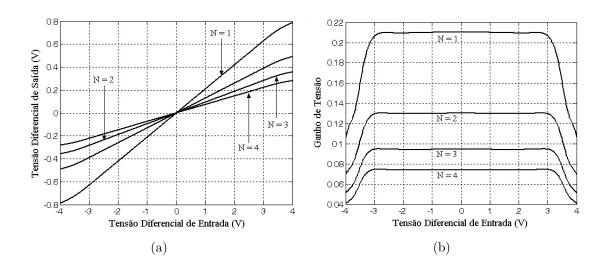

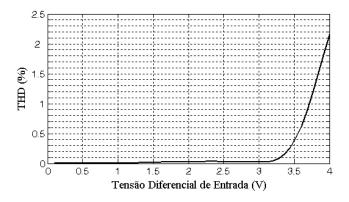

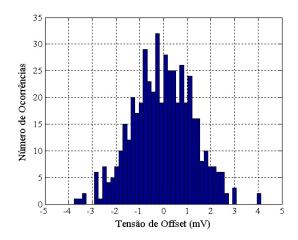

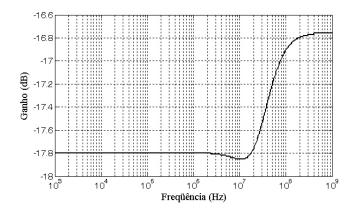

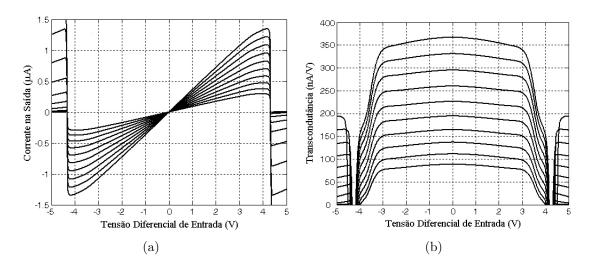

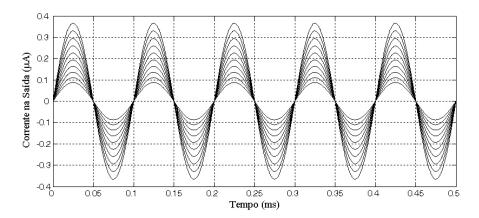

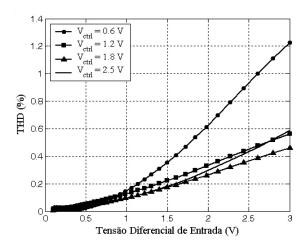

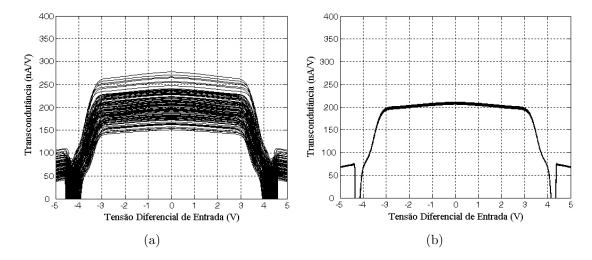

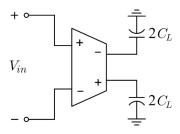

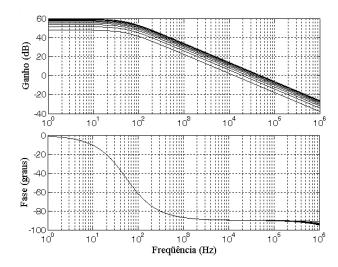

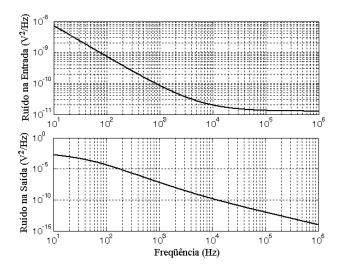

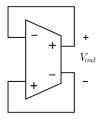

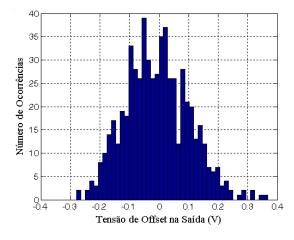

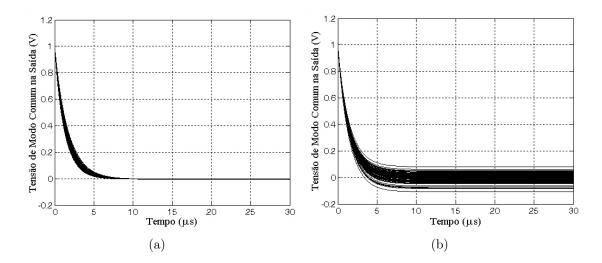

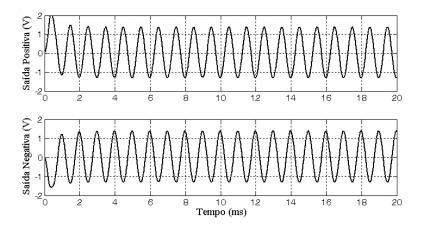

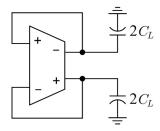

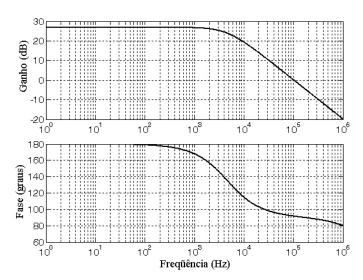

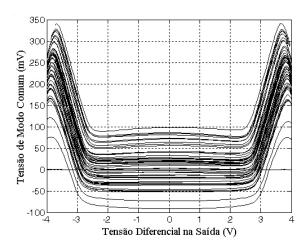

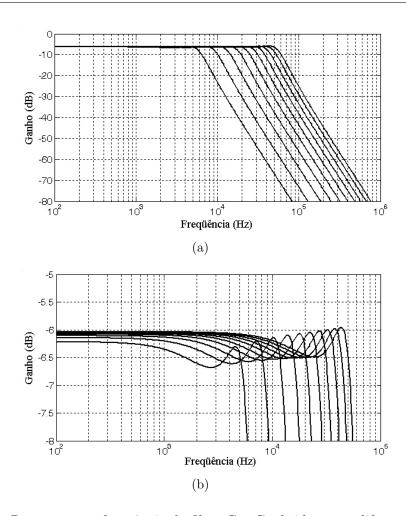

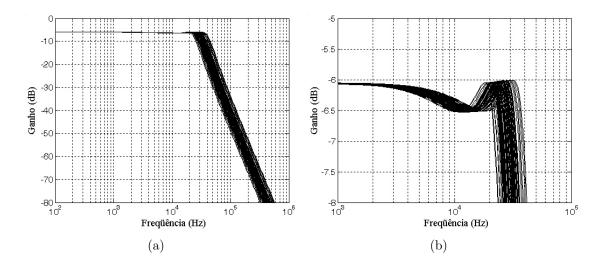

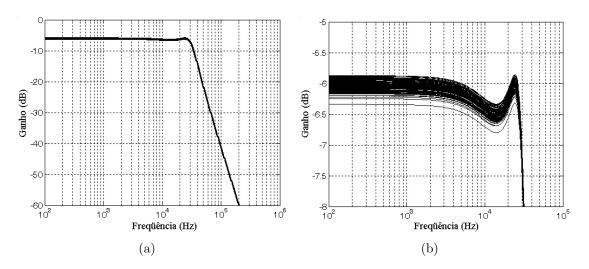

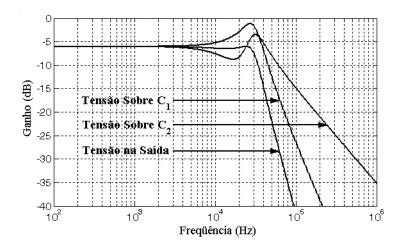

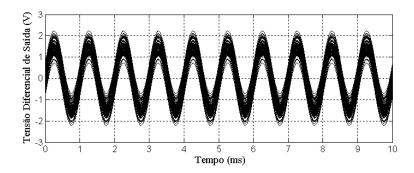

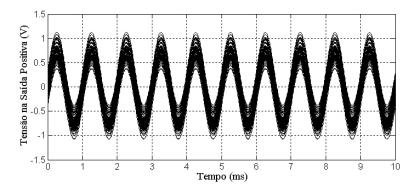

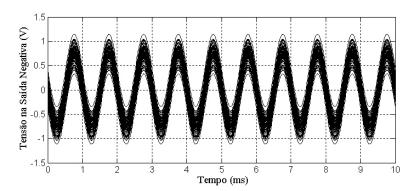

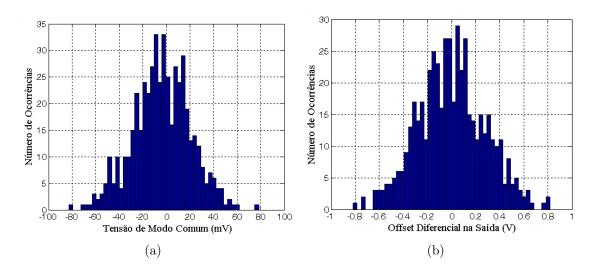

Por outro lado, o limite superior de um denominador deve ser o menor inteiro  $M_U$  tal que exista garantidamente pelo menos um inteiro  $N_D < M_U$  que produza um erro na resposta em freqüência do filtro dentro dos limites aceitáveis apresentados na Fig. II.10.